## **Getting Ahead with...**

# Broadband Macromodeling with IdEM

- Speaker: Michelangelo Bandinu

- ▶ Start time: 8 am PT, 11 am ET, 5 pm CET

- Audio will be broadcast through your computer speakers or headphones (no need to teleconference)

- ▶ In case of audio broadcast failure please use dial-in numbers from your registration email

- ▶ There will be no audio until the scheduled start time.

- A recording will be made available, you will be notified by email

- ► More information: <u>www.cst.com/webinars</u>

## Broadband Macromodeling with IdEM

Michelangelo Bandinu

## Outline

- Introduction to Macromodeling

- Passivity and Causality

- ☐ IdEM flow

- Demo: building macromodels with IdEM

- An application

#### **IdemWorks**

- ☐ IdemWorks was born as SpinOff from Politecnico di Torino, Italy

- ☐ Founded in 2007

- Mission: IdemWorks provides modeling tools and services for electronic design automation flows, helping hardware manufacturers to produce better products with a reduced time to market.

- ☐ Customers: Leading worldwide companies in the computer, networking, communications, consumer electronics, and automotive markets.

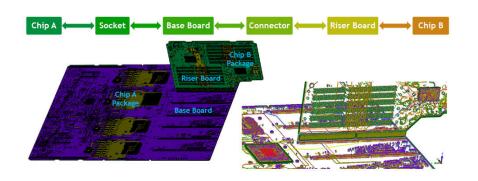

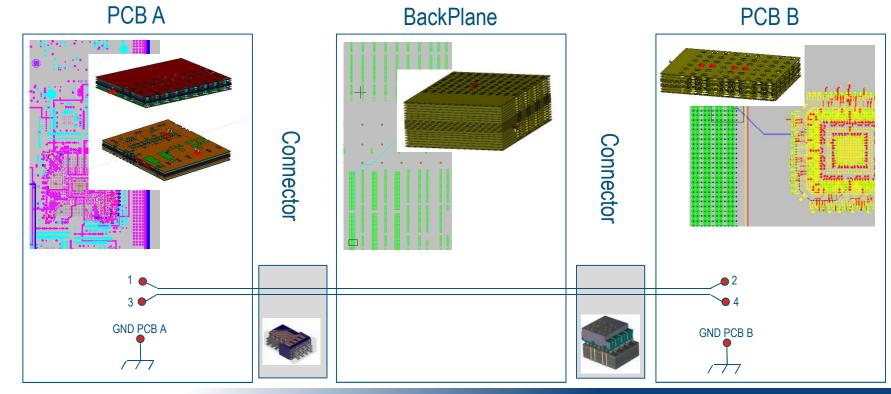

## Designing a complex high-speed link

- □ Data transmission: integrity of the signal through lines, bends, vias, connectors, transitions, ...

- **Need modeling for:** coupling, dispersion, losses, delays, discontinuities, power/ground structures, nonlinear terminations, ...

## The main objective

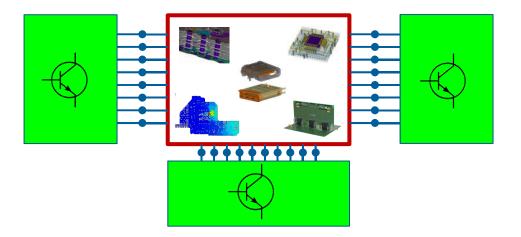

- ☐ Efficient Signal and Power integrity analysis requires **reliable** and **accurate** models both in pre-layout and post-layout phases.

- Main Objective: enabling fast and accurate circuit-level simulations.

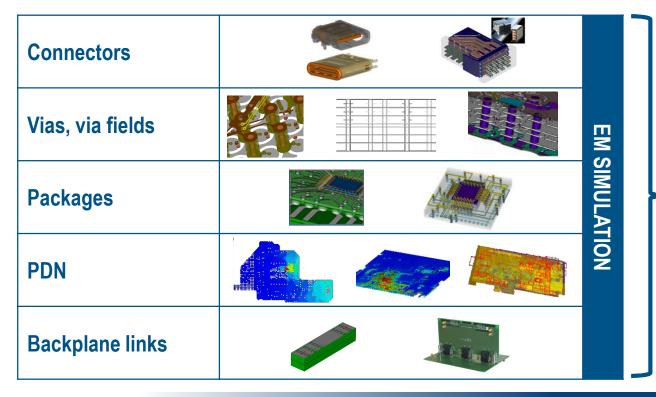

### Interconnects: showcase

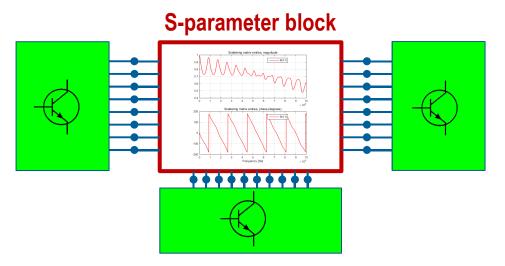

## S-parameter (tabulated)

## Frequency and Time domain "interplay"

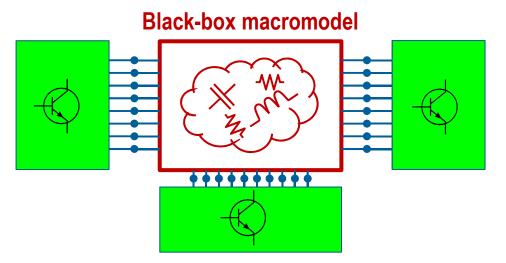

□ Electrical interconnect characterizations are typically available in the **frequency-domain**, often in terms of scattering parameters. Conversely, system-level simulations require **time-domain** analysis due to the presence of nonlinear driver/receiver circuitry.

## Frequency and Time domain "interplay"

□ Electrical interconnect characterizations are typically available in the **frequency-domain**, often in terms of scattering parameters. Conversely, system-level simulations require **time-domain** analysis due to the presence of nonlinear driver/receiver circuitry.

## Frequency and Time domain "interplay"

□ Electrical interconnect characterizations are typically available in the **frequency-domain**, often in terms of scattering parameters. Conversely, system-level simulations require **time-domain** analysis due to the presence of nonlinear driver/receiver circuitry.

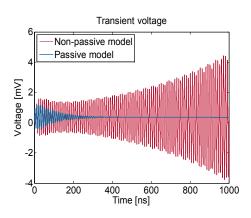

## Passivity and causality: requirements

□ SI/PI analysis requires **PASSIVE** and **CAUSAL** models to enable reliable and fast system level simulations

- PASSIVITY: Electrical interconnects never amplify signals. Non-passive models lead to time-domain convergence problems and are non physical

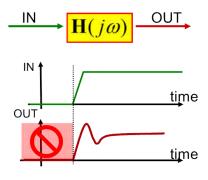

- □ CAUSALITY: Electrical interconnects never provide a response that anticipates in time their excitations

# DS.COM/SIMULIA © Dassault Systèmes | 3/3/2017 | ref.: 3DS Document 2018

## Passivity and causality issues: why?

| Ш | when data come from | measurements the | passivity/causality | violations may | be due to: |

|---|---------------------|------------------|---------------------|----------------|------------|

|   |                     |                  |                     |                |            |

- improper calibration and de-embedding

- □ human mistakes

- measurement noise

- ☐ When data come from **simulations** the passivity/causality violations may be due to:

- poor meshing

- ☐ inaccurate solver

- bad models or assumptions on material properties

- (e.g. dielectrics with a tandelta which is constant in frequency)

- human mistakes

- improper use of data interpolation or extrapolation features of the solver

- ☐ (often based on ill-defined and non-causal interpolation rules)

- putting together results from two solvers

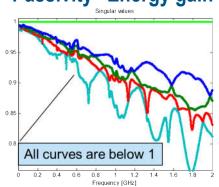

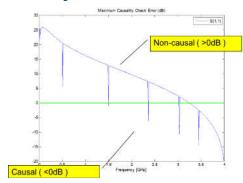

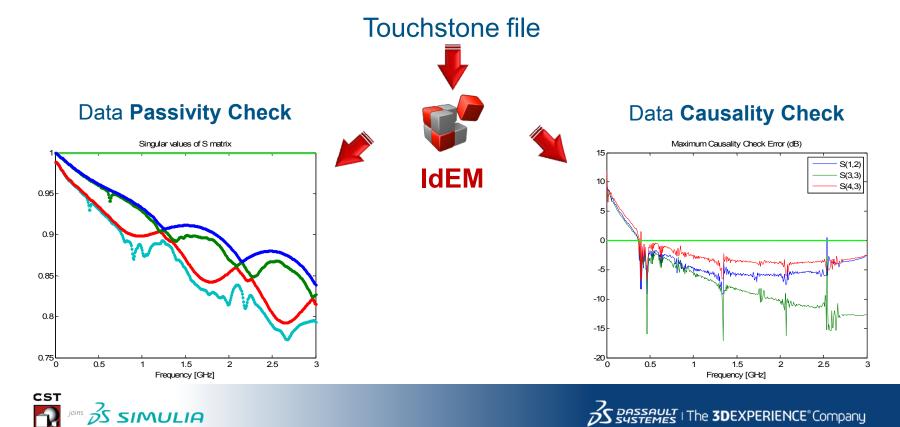

## Validation of S-parameter Data

- "*Energy gain*" is a necessary, but not sufficient condition for passivity.

- Causality is a prerequisite for Passivity.

#### Passivity "Energy gain"

#### Causality "Hilbert-based check"

- ☐ All the models generated by IdEM are **CAUSAL** by construction. The causality condition is enforced during the macromodel generation.

- ☐ The model is also **PASSIVE** if the passivity enforcement has been enforced by IdEM.

## IdEM: bridging the gap

#### Frequency-domain

$$\begin{bmatrix} S_{11} & S_{12} & S_{13} & S_{14} \\ S_{21} & S_{22} & S_{21} & S_{24} \\ S_{31} & S_{32} & S_{33} & S_{24} \\ S_{41} & S_{42} & S_{43} & S_{44} \end{bmatrix}$$

#### Time-domain

#### **IdEM** validates S-parameters:

- ✓ PASSIVITY check

- ✓ Energy gain

- ✓ CAUSALITY check

#### **IdEM** delivers reliable models:

- ✓ Passive

- ✓ Causal

- ✓ Stable

- ✓ Accurate

- ✓ SPICE-ready

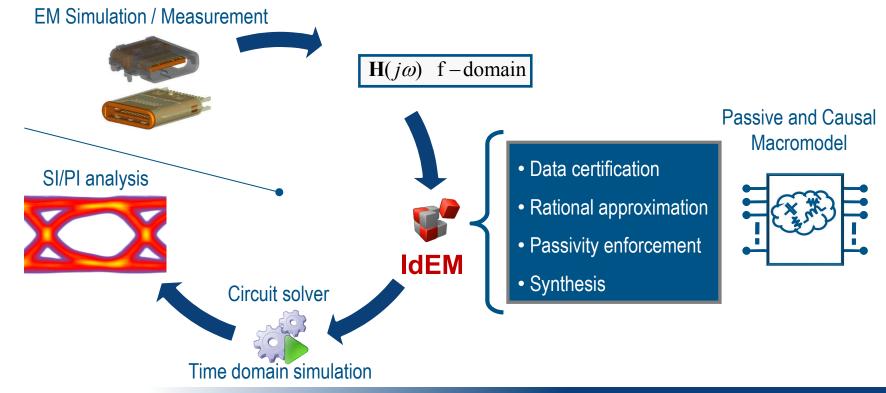

## IdEM-based simulation flow

## The IdEM flow

#### IdEM work-flow

- 1. Import Touchstone file

- 2. Check data passivity

- 3. Check data causality

- Model build

- 5. Check model passivity

- 6. Enforce model passivity

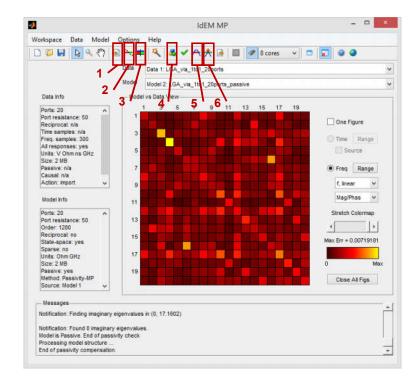

## IdEM: unique data certification engine

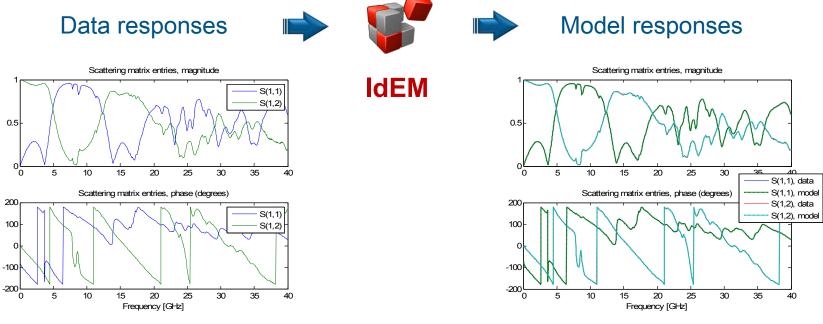

## IdEM: model generation

**Accurate – Stable – Causal – Passive**

## IdEM: model synthesis

#### IdEM spice subcircuit

```

* STATE-SPACE REALIZATION

* This file is automatically generated *

***********

* Created by IdEM

**********

* Interface (ports specification) *

.subckt passive_circuit

+ a 1 a 2 a 3 a 4 ref

************

* Main circuit connected to output nodes

* Port 1

VI 1 a 1 NI 1 0

GC_1_1 b_1 NI_1 NS_1 0 2.5693083123524896e-001

GC 1 2 b 1 NI 1 NS 2 0 -5.6469170068284752e-002

GC 1 3 b 1 NI 1 NS 3 0 4.8926190008399095e-002

GC 1 4 b 1 NI 1 NS 4 0 -5.2083718292784568e-002

GC_1_5 b_1 NI_1 NS_5 0 1.4574389378577475e-005

GC_1_6 b_1 NI_1 NS_6 0 -2.1775247527891126e-005

```

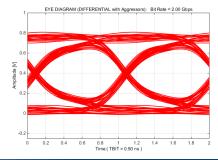

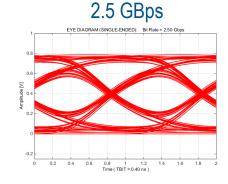

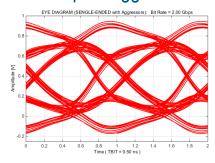

## Time domain simulation

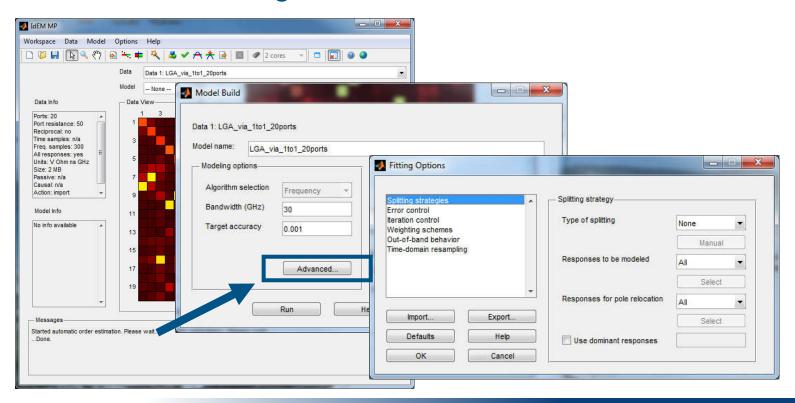

## Building macromodels with IdEM

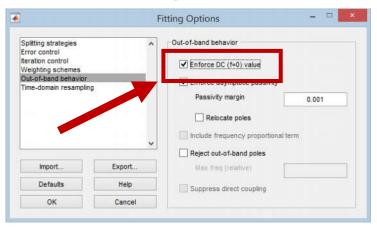

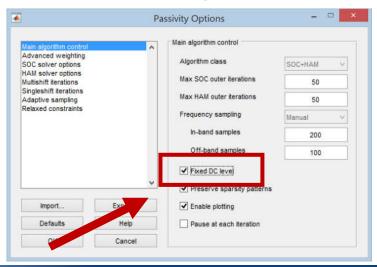

## Model generation with DC point constraints

**Advanced feature:** the DC response of a model can be constrained to the data DC point value. The DC point can be preserved both during fitting and passivity enforcement.

#### **Advanced fitting options**

#### **Advanced passivity options**

## Multi-processing

IdEM enables multi-processing capabilities that allows handling even large structures with an extraordinary speed-up in simulation runtime.

| Benchmark   | N. ports | N. samples | State-space | CPU time  | IdEM MP |

|-------------|----------|------------|-------------|-----------|---------|

|             | 48       | 690        | 1248        | Fitting   | 21s     |

| Benchmark 1 |          |            |             | Passivity | 6s      |

|             |          |            |             | Total     | 27s     |

|             | 98       | 189        | 6664        | Fitting   | 1m 50s  |

| Benchmark 2 |          |            |             | Passivity | 6m 45s  |

|             |          |            |             | Total     | 8m 35s  |

|             | 83       | 1228       | 1826        | Fitting   | 48s     |

| Benchmark 3 |          |            |             | Passivity | 55s     |

|             |          |            |             | Total     | 1m 43s  |

|             | 148      | 364        | 4440        | Fitting   | 43s     |

| Benchmark 4 |          |            |             | Passivity | 3m 8s   |

|             |          |            |             | Total     | 3m 51s  |

|             | 165      | 348        | 8250        | Fitting   | 2m 12s  |

| Benchmark 5 |          |            |             | Passivity | 2m 22s  |

|             |          |            |             | Total     | 4m 34s  |

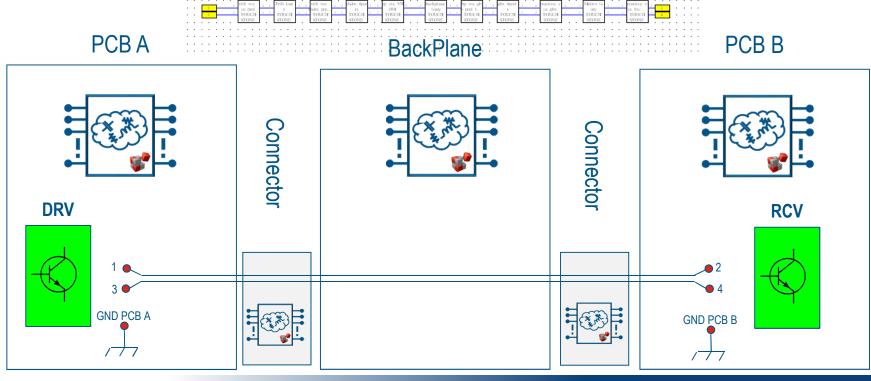

## Application: interconnect link

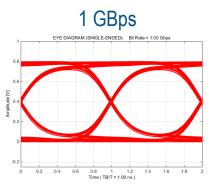

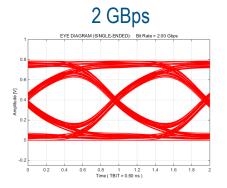

## Application: interconnect link

## Application: interconnect link

2 GBps + aggressors

#### 2 GBps + differential + aggressors