### T

# Altium Designer (build 7.x). Проект многослойной печатной платы:

## Проект многослойной печатной платы: правила топологии и результат их действия

В этой части статьи будут рассмотрены правила топологии проекта многослойной печатной платы и показаны результаты их взаимодействия.

Владимир Пранович, к. т. н.

pranovich@bsu.by

#### Задание правил топологии в РСВ-редакторе

Рассмотрим правила, непосредственно связанные с данным примером. Ниже будут представлены как сами правила, так и их действие при размещении элемента топологии в приведенном примере многослойной печатной платы. Сложные варианты или взаимодействие нескольких правил будут рассмотрены на конкретных примерах в соответствующих разделах.

Здесь приведем правила, написанные для данного примера проекта, в том порядке, в котором они следуют в редакторе PCB Rules and Constraints Editor. Представим все правила, начиная с низшего приоритета. Некоторые простые и идентичные по действию правила при этом опустим.

#### Раздел правил Electrical Clearance

Этот раздел — один из наиболее используемых при написании правил. Более того, правила именно этого раздела наиболее трудоемки в построении и в то же время самые важные, так как отвечают за качество печатной платы.

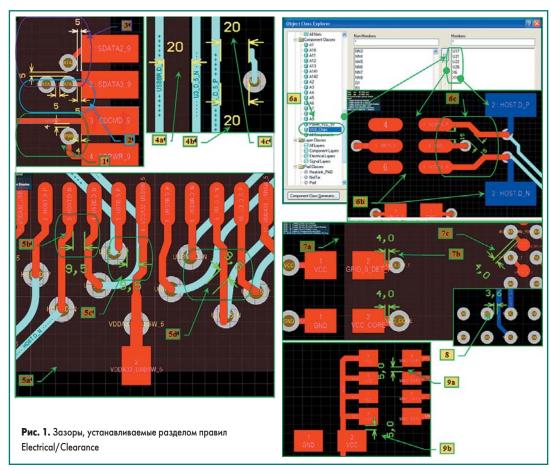

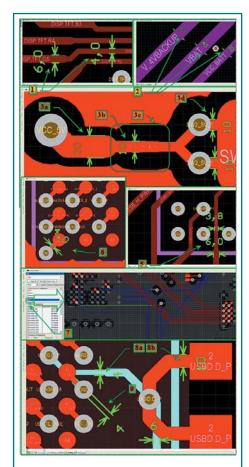

- 1. Имя правила Clearance\_NET\_to\_VIA. Оно устанавливает минимальный зазор между всеми проводящими элементами топологии и переходными отверстиями. В частности, на рис. 1 указаны два зазора: между переходным отверстием, принадлежащим цепи SDPWR\_9, и контактной площадкой и проводником, принадлежащими цепи SDCMD\_9. Текст правила:

- Первое условие **All**.

- Второе условие **IsVia**.

- Параметры: Different Net Only;

Minimum Clearance = 4 mil.

- Имя правила Clearance\_Via\_PAD\_SameNet. Оно устанавливает минимальный зазор между данным переходным отверстием и любым другим переходным отверстием или контактной площадкой посадочного места, которые принадлежат ОДНОЙ электрической связи. Правило не распространяется на свободные контактные площадки, введенные командой Place >> Pad. Оно предназначено для запрета «наложения» рядом стоящих переходных отверстий или запрета установки переходного отверстия вблизи контактной площадки компонента. Зазор между переходными отверстиями установлен выше, чем в предыдущем правиле. На рис. 1 указан зазор между переходным отверстием и контактной площадкой, а также между двумя переходными отверстиями, принадлежащими цепи SDATA3\_9. Текст правила:

- Первое условие IsVia Or IsComponentPad.

- Второе условие **IsVia**.

- Параметры: Same Net Only;

Minimum Clearance = 5 mil.

- 3. Имя правила Clearance\_Via\_PAD. Оно устанавливает минимальный зазор между данным переходным отверстием и любым другим переходным отверстием или контактной площадкой, которые принадлежат РАЗНЫМ электрическим цепям. На рис. 1 данный зазор указан для переходного отверстия, принадлежащего цепи SDATA2\_9, и переходного отверстия и контактной площадки, принадлежащих цепи SDATA3\_9. Заметим: так как параметры зазоров в этом и предыдущем правиле одинаковы, правило можно (и лучше) объединить. Однако мы не станем этого делать, поскольку здесь принципиально показать суть действия правила. Итак, текст правила:

- Первое условие IsVia Or IsPad.

- Второе условие IsVia.

- Параметры: Different Net Only;

Minimum Clearance = 5 mil.

- 4. Имя правила ClearanceDiffPairDiffer. Оно устанавливает минимальный зазор между проводниками, принадлежащими дифференциальным линиям, и любыми другими проводниками. Величина данного зазора много выше, чем установленный зазор по умолчанию, и в этом проекте составляет 20 mil. На рис. 1 данный зазор указан:

- а) между двумя проводниками, принадлежащими PA3HЫМ дифференциальным линиям (USBBR.DP\_P и U3\_D\_5\_N). Отметим, что данное правило не распространяется на проводники, принадлежащие одной дифференциальной линии. Так, расстояние между проводниками U3\_D\_5\_N и U3\_D\_5\_N меньше и будет определяться другим правилом.

- b) расстояние до переходного отверстия. На рис. 1 приведено изображение внутреннего слоя печатной платы, и на этом слое находятся проводники дифференциальной линии и проекция переходного

- отверстия. Обратите внимание: в данном случае переходное отверстие не имеет выхода металлизации на указанном слое, и поэтому расстояние определяется не значением диаметра переходного отверстия (параметр **Diameter**), а непосредственно диаметром его отверстия (параметр **Hole**).

- с) между ближним проводником дифференциальной линии и любым другим проводящим объектом, в частности указан проводник, принадлежащий другой цепи.

Итак, текст правила таков:

- Первое условие InAnyDifferentialPair.

- Второе условие All.

- Параметры: Different Net Only;

Minimum Clearance = 20 mil.

- 5. Имя правила Clearance\_DiffPairFanout4. Предыдущее правило устанавливает такое значение величины зазора между дифференциальными линиями и другими элементами, которое не позволит сделать отвод проводников этих линий от контактных площадок компонентов, так как расстояние между площадками уже меньше этой величины. Это и последующие правила укажут иные значения зазора между проводниками дифференциальной линии вблизи отвода от компонентов. Отметим, что дополнительно для решения указанной проблемы у нас созданы (при автоматической генерации) и размещены на РСВ специальные области (ROOM). Именно этим правилом зададим новый зазор внутри этих ROOM для коротких проводников.

**Примечание.** Отвод проводников от контактных площадок микросхем на внешних слоях должен быть как можно короче с переходом на внутренний слой. На внутреннем слое в области указанных **ROOM** первый отрезок отвода проводника также всегда будет коротким.

Итак, текст следующего правила будет таким:

- Первое условие InAnyDifferentialPair.

Для всех объектов, принадлежащих дифференциальным линиям.

- Второе условие isTrack And (TraceLength < 100) And (WithinRoom('A2') Or WithinRoom('A4') Or WithinRoom('A5') Or WithinRoom('A9')). Для всех проводников типа Track с длиной не более 100 mil и находящихся в любой из перечисленных Room.</li>

- Параметры: Different Net Only;

Minimum Clearance = 9,5 mil.

- В частности, на рис. 1 указаны:

- a) граница **ROOM**, в зоне которой действует правило.

- b) проводники, принадлежащие разным дифференциальным линиям и расположенные на слое TOP, минимальный зазор между которыми подчиняется данному правилу.

- с) зазор на слое TOP (красный цвет) между переходным отверстием, которое принадлежит цепи дифференциальной линии, и проводником другой электрической цепи, выдержан в соответствии с данным правилом.

- d) зазор на внутреннем слое (голубой цвет) между двумя дугами проводников от разных дифференциальных линий.

- 6. Имя правила Clearance\_DiffPairFanout3. Ряд компонентов и соединителей, к которым подходят дифференциальные линии, имеют все же достаточное расстояние между выводами, чтобы обеспечить более жесткое требование по зазору между дифференциальными линиями и другими объектами топологии. Условия этого правила можно записать без перечисления всех таких компонентов, а указать лишь их класс. В подобных случаях в этом проекте такие компоненты всегда объединены в одном из классов. Текст правила будет таким:

- Первое условие InAnyDifferentialPair And (WithinRoom('A2') Or WithinRoom('A4') Or WithinRoom('A5') Or WithinRoom('A8') Or WithinRoom('A9')). Для всех объектов, принадлежащих дифференциальным линиям и находящихся в любой из перечисленных Room.

- Второе условие ((isPad And InComponentClass('USB\_Chips')) Or isVia). Для всех контактных площадок компонентов класса USB\_Chips и любых переходных отверстий.

- Параметры: Different Net Only;

Minimum Clearance = 15 mil.

- В частности, на рис. 1 указаны:

- а) окно Object Class Explorer, в котором выделены класс компонентов USB\_Chips и его члены;

- b) компоненты U27 (сторона ТОР, красный цвет) и X6 (сторона Bottom, синий цвет);

- с) зазоры между:

- контактной площадкой дифференциальной линии электрической цепи HOST.D\_P и контактной площадкой цепи GND;

- переходным отверстием на слое ТОР и проводником дифференциальной линии.

- Опустим описание идентичных правил для дифференциальных линий, определяющих проверку зазоров в ближней зоне от источника сигнала или от потребителя. Укажем далее другие правила:

- 7. Имя правила Clearance\_Via\_PAD\_BGA\_SameNet. В зоне BGA-компонентов с шагом 0,65 мм зададим минимально возможный зазор между переходным отверстием и контактной площадкой для одной и той же цепи. Это правило позволит сделать при трассировке операцию Fanout для данных компонентов с требуемым зазором.

- Первое условие (IsVia Or IsComponentPad)

And (WithinRoom('A2') Or WithinRoom('A4')

Or WithinRoom('A8')). Для переходных отверстий и площадок в данных Room.

- Второе условие isVia. Для всех переходных отверстий.

- Параметры: Same Net Only;

Minimum Clearance = 4 mil.

- В частности, на рис. 1 указаны:

- a) граница Room('A2');

- b) зазор между контактной площадкой конденсатора и переходным отверстием в зоне вышеуказанной **Room**;

- с) зазоры между контактной площадкой компонента в BGA-корпусе и переходным отверстием, установленным вручную.

#### Технологии в электронной промышленности, № 8′2008

Рис. 2. Зоны, отмеченные в слое KeepOut

**Примечание.** Для таких компонентов операцию **Fanout** будем применять с автоцентрированием переходных отверстий, однако об этом подробнее скажем далее, в отдельном разделе правил.

- 8. Имя правила Clearance\_Via\_PAD\_BGA. В зоне BGA-компонентов с шагом 0,65 мм зададим значение зазора таким, чтобы дорожка минимальной ширины могла пройти между двумя соседними контактными площадками BGA-корпуса или переходными отверстиями под корпусом. Для корпуса с шагом 0,65 мм и шириной дорожки 4 mil значение зазора составит 3,6 mil = 0,914 мм, что немного превышает разрешенное значение допуска по 5-му классу. Однако его придется оставить, иначе мы не сможем сделать отводы от контактных площадок второго ряда BGA-компонента или проложить проводники между переходными отверстиями на внутренних слоях. Эту зону следует при заказе указать производителю печатных плат, для того чтобы были предприняты особые приемы для достижения качества печатной платы в указанной зоне.

- Первое условие (IsVia Or IsPad) And (WithinRoom('A2') Or WithinRoom('A4') Or WithinRoom('A8')). Для всех переходных отверстий и контактных площадок в указанных Room.

- Второе условие IsElectrical. Для любых проводников, принадлежащих какой-либо электрической цепи.

- Параметры: Different Net Only;

Minimum Clearance = 3,6 mil.

На рис. 1 данный зазор указан для переходного отверстия и дорожки на слое 1\_**Bottom**.

Имя правила — Clearance\_SMT\_pads. Задание зазора между двумя контактными площадками компонентов для поверхностного монтажа.

- Первое условие IsSMTPin. Указывает на принадлежность типу контактной площадки. В данном случае это площадка компонента для поверхностного монтажа.

- Второе условие **IsSMTPin**.

- Параметры: Different Net Only;

Minimum Clearance = 5 mil.

Правило распространяется как на зазоры между соседними площадками одного компонента (9а), так и на площадки, принадлежащие разным компонентам (9b).

- 10. Имя правила Clearance\_toKeepOut. Определим зазор между объектами в слое KeepOut и элементами топологии. Отметим еще раз, что в данном примере в этом слое будут отмечены как зона вблизи границ печатной платы, так и другие зоны, необходимые для технологических работ. В этом случае там будут обозначены непосредственно границы зоны, не требующие дополнительного зазора. Однако обратим внимание: зазор с нулевым значением разрешает пересечение этих границ, и для того, чтобы избежать этого, следует указать минимальное значение, например 1 mil. Правило будет таковым:

- Первое условие All. Указывает на принадлежность типу контактной площадки, в данном случае это площадка компонента для поверхностного монтажа.

- Второе условие **IsKeepOut**.

- Параметры: Any Net;Minimum Clearance = 1 mil.

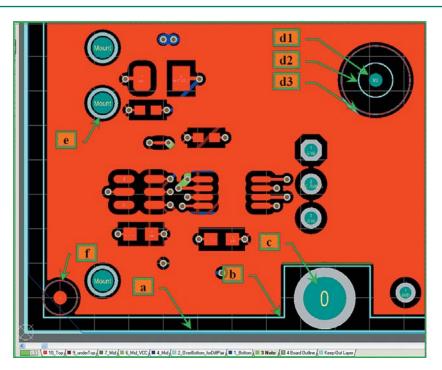

В частности, на рис. 2 указаны следующие объекты:

а) контур платы. Он создан линиями в отдельном механическом слое и продублирован в слое **KeepOut** еще на первоначальной стадии проектирования печатной платы при определении ее габаритов.

- b) контур в слое **KeepOut**. Он выполнен на стадии согласования крепежных отверстий и других областей запрета размещения компонентов и топологии на всех слоях печатной платы. Ширина линий и этого контура, и контура платы модифицирована для лучшего отображения обоих контуров на рис. 2. Для запрета топологии между данными контурами зазор между ними должен быть меньше указанного в правилах, в противном случае нужно увеличить ширину линий или применить закрашенные области (**Place** >> **Fill**) и т. п.

- с) крепежное отверстие. В данном случае оно внесено на печатную плату командой **Place** >> **PAD**. Зона запрета вокруг данного отверстия создана в общем контуре (см. пункт b), так как это отверстие находится на краю печатной платы.

- d) d1 непосредственно крепежное отверстие одного из компонентов платы, а именно индикатора. Отверстие не металлизировано и предназначено для пластмассового штыря. d2 — контур запрета трассировки вокруг данного отверстия для всех слоев сделан в слое KeepOut. d3 — элемент, устанавливаемый в данное отверстие, он имеет внешний диаметр значительно больше диаметра самого отверстия в печатной плате. Здесь указан в слое 10\_ТОР контур со свойством KeepOut, определяющим запрет топологии только на верхнем (10\_ТОР) слое. Свойства данного контура проанализируем при рассмотрении примера топологий.

- е) крепежное отверстие одного из элементов. Не имеет дополнительных ограничений, зона запрета выполнена только контуром в слое **KeepOut**.

- f) Global Fiducial. Данные метки имеют запрет только на верхнем слое, соответственно контур выполнен в слое 10\_TOP со свойством KeepOut.

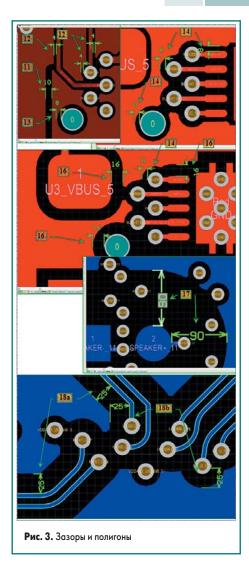

На рис. 3 представлен результат действия правил для указания зазора между полигоном и другими объектами топологии.

- 11. Имя правила Clearance\_MidLay\_Poly2Poly. Оно устанавливает зазор между двумя полигонами разных электрических цепей на внутренних слоях. Зазор задан увеличенный, так как обычно эти цепи принадлежат классам цепей питания компонентов или имеют протяженную совместную границу. Текст правила следующий:

- Первое условие IsCopperRegion.

Для области внутри полигона.

- Второе условие InPoly And OnMid.

Указаны объект (полигон) и место (внешние слои).

- Параметры: **Different Net Only**; **Minimum Clearance** = 10 mil.

- 12. Имя правила Clearance\_MidLay\_Poly. Оно устанавливает зазоры на всех внутренних слоях между полигоном и другими объектами топологии. На рис. 3, в частности, указаны зазоры до Track и Via на слое 9\_underTOP. Текст правила следующий:

- Первое условие IsPad or IsTrack Or IsArc Or IsVia. Перечислены типы объектов.

- Второе условие InPoly And OnMid.

Указаны тип второго объекта и слой, где он находится.

- Параметры: Different Net Only; Minimum Clearance = 4 mil. Величина зазора минимальная в соответствии с требованиями выбранного класса печатной платы.

- 13. Имя правила Clearance\_MidLay\_Poly2. Оно устанавливает зазор на всех внутренних слоях между полигоном и контактными площадками большого размера. Текст правила следующий:

- Первое условие IsPad And ((PadXSize\_ AllLayers > 30.0) Or (PadYSize\_AllLayers > 30.0)). Указан тип объектов.

- **Примечание:** обратите особое внимание, в выражении не используется размерность, по умолчанию в данном проекте она всегда только mil.

- Второе условие InPoly And OnMid.

- Параметры: Different Net Only; Minimum Clearance = 8 mil. Установлено увеличенное значение зазора.

- 14. Имя правила Clearance\_OutLay\_Poly. Оно устанавливает зазор до металлизации полигона на внешних слоях. Так как это сторона монтажа, зазор установлен увеличенным. На рис. 3 показана та же область

печатной платы, но для стороны **10\_TOP**. Текст правила следующий:

- Первое условие All.

- Второе условие inPoly and OnOutside.

Указаны объект (полигон) и место расположения (внешние слои).

- Параметры: Different Net Only; Minimum Clearance = 8 mil.

- 15. Имя правила Clearance\_OutLay\_Poly2Poly. Правило аналогично 11 пункту, но для внешних слоев и, соответственно, определяет больший зазор. На рис. 3 не показано. Текст правила следующий:

- Первое условие **IsCopperRegion** (для области полигонов).

- Второе условие InPoly And OnOutside.

- Параметры: **Different Net Only**; **Minimum Clearance** = 20 mil.

- 16. Имя правила Clearance\_PolyOutside\_ **ToPad.** Правило также аналогично 11 пункту. Устанавливает увеличенный зазор до контактных площадок, так как последние открыты (без маски). Это правило необходимо для гарантированного закрытия полигонов маской и, соответственно, для повышения качества печатной платы. Обратите внимание на вид полигонов до (сноска 14) и после введения данного правила — последнее правило не затрагивает зазоров до переходных отверстий (они в данном проекте будут закрыты маской). Однако вследствие увеличенного зазора до контактных площадок могут образовываться дополнительные области, не заполненные полигоном. Текст правила следу-

- Первое условие InPoly And OnOutside.

- Второе условие **IsPAD**.

- Параметры: Different Net Only; Minimum Clearance = 16 mil.

- 17. Имя правила Clearance\_Poly2\_to\_ EAS3P127A. Здесь указано правило для специфического компонента, а именно внешнего динамика, подключение которого необходимо проводить при сборке с помощью пайки гибких выводов. Текст правила следующий:

- Первое условие IsPad And HasFootprint ('EAS3P127A — V2'). Указано условие для всех контактных площадок приведенного посадочного места. Отметим, что такая запись правила хоть и сложнее, но предпочтительней, нежели указание номера (Designator) компонента в правиле, поскольку данный номер при операции перенумерации компонентов может изменить свое значение, а имя посадочного места остается неизменным.

- Второе условие InPoly And OnOutside.

Также отметим, что можно было указать только ту сторону, с которой производится ручная пайка гибких выводов.

Однако в данном случае контактные площадки находятся с одной стороны, и правила действуют одинаково.

- Параметры: Different Net Only;

Minimum Clearance = 90 mil.

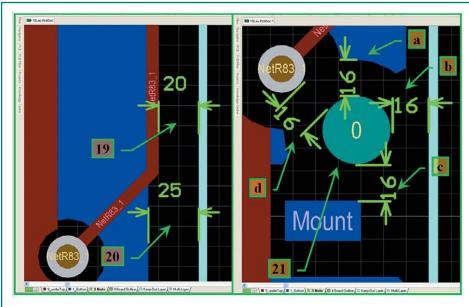

- 18. Имя правила Clearance\_PolyonBottom2Diff. При определении Layer Stack (стек слоев)

[1, рис. 4] для данного проекта слой 2\_OverBottom\_forDiffPair был предназначен исключительно для дифференциальных линий, и он находится между слоем 3\_Ground\_Bottom типа PLANE (слой для электрической цепи GND) и нижним слоем. Расчет параметров дифференциальных цепей мы будем производить, считая, что слой GND есть только с одной стороны дифференциальной линии, а именно со стороны слоя **PLANE**. В таком случае заливку полигонов на нижнем слое печатной платы мы должны запретить. Обратите внимание: правило действует только для проводников (копия трассировки дифференциальных линий слоя 2\_OverBottom\_ forDiffPair на слой 1\_Bottom) с установленным флагом KeepOut (см. сноски а и b на рис. 4), зазор между переходным отверстием дифференциальной линии и полигоном это правило не определяет. Однако такой подход к очистке покрытия от меди на соседних слоях мы рассмотрим подробнее в разделе, посвященном исключительно дифференциальным линиям. Текст правила следующий:

- Первое условие inPoly and OnLayer ('1\_Bottom').

- Второе условие **IsKeepOut**.

- Параметры: **AnyNet**; **Minimum Clearance** = 25 mil.

- 19. Имя правила Clearance\_to\_Keep-Out. Правило введено нами для учета возможностей производителя [1]. Результат действия правила представлен на рис. 4. Текст правила следующий:

- Первое условие All.

- Второе условие OnLayer('Keep-Out Layer'). Для всего на слое Keep-Out.

- Параметры: Any Net для любых цепей; Minimum Clearance = 20 mil.

- Имя правила Clearance\_OnOutside\_Keep-Out. Аналогично, но для внешней стороны печатной платы. Текст правила следующий:

- Первое условие OnOutside. Для всего на внешних слоях.

- Второе условие OnLayer('Keep-Out Layer').

- Параметры: Any Net;

Minimum Clearance = 25 mil.

- 21. Имя правила Clearance\_KeepOut\_To\_ Hole. Аналогично, но для сквозных отверстий. Текст правила следующий:

- Первое условие OnLayer('Keep-Out Layer').

- Второе условие **HoleSize**.

- Параметры: Any Net;

Minimum Clearance = 16 mil.

В частности, на рис. 4 показано крепежное отверстие без металлизации и указаны следующие зазоры:

- а) до полигона на нижнем слое;

- b) до линии на слое **KeepOut**;

- с) до контактной площадки на нижнем слое;

- d) до переходного отверстия.

Простые и повторяющиеся правила из этого раздела мы опустили и, если возникнет необходимость, укажем их особо.

Рис. 4. Зазоры для KeepOut HoleSize

#### Разделы правил Electrical/Short-Circuit и Electrical/Un-Routed Net

В данном примере дополнительных правил для этих разделов создавать не будем.

#### Раздел правил Routing Widht

Этот раздел правил также рассмотрим детально.

- 1. Имя правила **Width\_All**. Ширина проводников по умолчанию:

- Условие All.

- Параметры Width = 4 mil; Preferred Width = 5 mil; Max Width = 6 mil.

В частности, на рис. 5 показан проводник с максимально допустимой для него шириной и ее снижением до минимального значения в «узком» месте.

- 2. Имя правила Width\_PowerBus. Оно устанавливает увеличенное значение ширины проводников, принадлежащих шинам питания, длина которых больше заданной величины. На рис. 5 указан фрагмент слоя 4\_MID\_VCC. Правило таково:

- Условие ((InNetClass('PowerGlobal')

Or InNetClass('PowerLoop') Or InNetClass ('PowerLocal')) And (TraceLength > 170)).

Перечислены классы цепей питания.

- Параметры Width = 20 mil; Preferred Width = 25 mil; Max Width = 40 mil.

- 3. Имя правила Width\_ShortPw. Оно устанавливает значение ширины проводников, принадлежащих классам цепей питания, длина которых меньше заданной величины. Как правило, это отводы от шины к ножкам компонентов. Правило будет таким:

- Условие ((InNetClass('PowerGlobal')

Or InNetClass('PowerLoop') Or InNetClass ('PowerLocal')) And (TraceLength <= 170)).</li>

- Параметры для наружных слоев, слоя 6\_MID\_MCC и остальных слоев соответственно: Width = 5, 5 и 5 mil; Preferred Width = 6, 20 и 8 mil; Max Width = 40, 40 и 40 mil. Нижняя граница значения выбрана такой, чтобы обеспечить подвод проводника к компоненту с минималь-

ным шагом выводов. Заметьте, в этом правиле мы впервые определили разные параметры для разных слоев Layer Stack. На рис. 5 отмечены следующие области и объекты для слоя 10\_TOP:

- а) проводник цепи VCC\_5V шины питания (класс 'PowerGlobal') шириной 20 mil;

- b) проводник той же цепи при подключении к PAD топологической перемычки шириной 10 mil:

- с) область, где расположена топологическая перемычка, которая содержит два наложенных с частичным перекрытием друг на друга PAD, принадлежащие двум разным цепям: цепи VCC\_5V шины питания (класс 'PowerGlobal') и цепи SW2\_5V\_1 класса 'PowerLocal';

- d) подключение цепи SW2\_5V\_1 к контактной площадке компонента произведено двумя проводниками шириной по 10 mil. Обратите внимание (хотя это не относится к данному правилу): каждый проводник имеет собственное переходное отверстие для подключения к слою PLANE, что сделано для снижения значения максимального тока, протекающего через переходное отверстие.

- 4. Имя правила Width\_DifPair. Оно устанавливает значение ширины проводников, принадлежащих шинам питания, длина которых меньше заданной величины. Обычно это отводы проводников от контактных площадок компонентов. Правило будет таким:

- Условие InAnyDifferentialPair.

- Параметры Width = 6 mil; Preferred Width = 6 mil; Max Width = 10 mil для внутренних слоев. Нижняя граница значения выбрана такой, чтобы обеспечить подвод проводника к компоненту с минимальным шагом выводов.

- 5. Имя правила Width\_nexttoBGA. Оно устанавливает значение ширины проводников под элементами в BGA-корпусах с мелким шагом выводов. Правило устанавливает наи-

Рис. 5. Ширина проводников

более жесткие требования к минимальной ширине и зазорам в указанных областях. На рис. 5 отражена часть корпуса BGA-компонента и указан фрагмент вида слоя 9\_UndorTOP. Правило будет таким:

- Условие (TouchesRoom('A2') Or Touches-Room('A4') Or TouchesRoom('A8')). Для проводников, пересекающих указанные области (данные ROOM содержат области вокруг BGA-корпусов).

- Параметры для слоев представим в виде таблицы 1, однако отметим, что здесь задаются параметры только для сигнальных слоев.

- 6. Имя правила Width\_nexttoBGA\_Pw\_fanout. Оно устанавливает значение ширины коротких проводников питания для подвода к PAD корпусов BGA, а конкретно максимально возможную ширину проводников для подвода питания без нарушения требований класса печатной платы. Правило будет таким:

Таблица 1. Параметры для слоев (правило Width\_nexttoBGA)

| Layer                    | Width   | Preferred<br>Width | Max<br>Width |  |

|--------------------------|---------|--------------------|--------------|--|

| 10_Top                   | 3,8 mil | 10 mil             | 10 mil       |  |

| 9_underTop               | 3,8 mil | 4 mil              | 8 mil        |  |

| 7_Mid                    | 3,8 mil | 4 mil              | 8 mil        |  |

| 6_Mid_VCC                | 3,8 mil | 10 mil             | 40 mil       |  |

| 4_Mid                    | 3,8 mil | 4 mil              | 8 mil        |  |

| 2_OverBottom_forDiffPair | 3,8 mil | 6 mil              | 6 mil        |  |

| 1_Bottom                 | 3,8 mil | 10 mil             | 10 mil       |  |

- Условие (WithinRoom('A2') Or Within-Room('A4') Or WithinRoom('A8')) AND ((InNetClass('PowerGlobal') Or InNetClass-('PowerLocal')) And (TraceLength <= 170)).</li>

Для проводников цепей питания внутри данных областей, длина которых ограничена указанной величиной.

- Параметры для слоев представлены в таблице 2.

Таблица 2. Параметры для слоев (правило Width\_nexttoBGA\_Pw\_fanout)

| Layer                    | Width | Preferred<br>Width | Max<br>Width |  |

|--------------------------|-------|--------------------|--------------|--|

| 10_Top                   | 4 mil | 10 mil             | 40 mil       |  |

| 9_underTop               | 4 mil | 8 mil              | 40 mil       |  |

| 7_Mid                    | 4 mil | 8 mil              | 40 mil       |  |

| 6_Mid_VCC                | 4 mil | 20 mil             | 40 mil       |  |

| 4_Mid                    | 4 mil | 8 mil              | 40 mil       |  |

| 2_OverBottom_forDiffPair | 4 mil | 6 mil              | 40 mil       |  |

| 1_Bottom                 | 4 mil | 10 mil             | 40 mil       |  |

- 7. Имя правила Width\_DABuses. Оно устанавливает значение ширины для определенного класса цепей. В данном случае необходимо соблюдать ширину проводника этого класса на всех слоях, так как далее предполагается контролировать задержку в данных проводниках. На рис. 5 выделен фрагмент топологии цепей класса 'BUS', проводники которых имеют ширину в соответствии с данным правилом. Правило будет таким:

- Условие ((InNetClass('BUS') Or InNet-Class('UD') Or InNetClass('XA'). Перечислены типы классов.

- Параметры Width = 4 mil; Preferred Width = 4 mil; Max Width = 4 mil.

- Имя правила Width\_DiffFanout. Оно устанавливает значение ширины проводников дифференциальных линий, подключенных с одной из сторон к нескольким PAD разных компонентов. Правило будет таким:

- Условие InAnyDifferentialPair And OnOutside And (TraceLength <= 170) And (TouchesRoom('A5') Or TouchesRoom('A9')).

В частности, указаны класс, сторона и области, на которые распространяется правило, а также максимальная длина проводника.

- Параметры вводятся для всех слоев, но здесь приведем только для двух, где и могут находиться проводники дифференциальных линий, а именно 2\_OverBottom\_forDiffPair и 10\_Top:Width = 4 mil; Preferred Width = 5 и 10 mil; Max Width = 6 и 10 mil.

Заметим, это правило будет действовать только вблизи точек подключения проводников дифференциальных линий к PAD. Так, на рис. 5 указано:

- а) сужение проводника дифференциальной линии до ширины 4 mil для подвода к контактной площадке BGA-корпуса, с целью сохранения значения зазоров и ширины в пределах допуска пятого класса печатных плат;

- b) подключение на стороне **10\_Тор** с рассчитанной для этой стороны шириной проводника для дифференциальной линии;

- c) рассчитанная ширина дифференциальной линии в слое 2\_OverBottom\_forDiffPair.

- 9. Имя правила Width\_fanoutBGA. Оно устанавливает значение ширины для операции Fanout для нестандартных корпусов (не из списка имеющихся по умолчанию типов корпусов). Правило будет таким:

- Условие inBGA Or ((BigColumnCount >= 6) Or (BigRowCount >= 6)). Здесь указаны как стандартный тип корпусов, так и дополнительные условия для отнесения к такому же типу посадочных мест. В частности, указаны класс, сторона и области, на которые распространяется правило, а также максимальная длина проводника, на которую будет распространяться правило.

- Параметры такие же, как для пункта 3.

#### Раздел правил Routing/Routing Topology

Так как в примере автоматическая трассировка печатной платы не используется, ограничимся только двумя правилами, а именно:

- 1. Имя правила RoutingTopology. Для всех электрических цепей по умолчанию установим правило последовательного соединения проводниками контактных площадок. Правило будет таким:

- Условие All.

- Параметры: Topology=Daisy Simple.

- 2. Имя правила RoutingTopology\_Pwr. Для всех электрических цепей питания установим правило соединения по наиболее короткому пути. Правило будет таким:

- Условие InNetClass('PowerGlobal')

Or InNetClass('PowerLocal').

- Параметры: Topology=Shortest.

#### Раздел правил Routing/Routing Priority

Еще раз укажем, что в данном примере полностью автоматическая трассировка не используется, однако отдельные фрагменты сделаны в полуавтомате. Поэтому частично описан и данный раздел. Итак, в этом разделе установим следующие приоритеты:

- 1. Имя правила **RoutingPriority**. По умолчанию самый низкий приоритет:

- Условие All.

- Параметры: Routing Priority=4.

- 2. Имя правила RoutingPriority\_Power. Далее электрические цепи питания:

- Условие (InNetClass('PowerGlobal') Or InNetClass('PowerLocal')).

- Параметры: Routing Priority=3.

- 3. Имя правила RoutingPriority\_ADBUS. Далее электрические цепи некоторых классов, таких как шины адреса, данных и т. п.:

- Условие ((InNetClass('BUS') Or InNet-Class('UD') Or InNetClass('XA').

- Параметры: Routing Priority=2.

- 4. Имя правила RoutingPriority\_Diff. И, наконец, с наиболее высоким приоритетом для дифференциальных линий:

- Условие InAnyDifferentialPair.

- Параметры: Routing Priority=1.

#### Раздел правил Routing/Routing Layer

В соответствии с Layer Stack дополним назначение сигнальных слоев для топологии це-

**Таблица 3.** Назначение сигнальных слоев для топологии классов цепей

|                              | Имя правила, условие и флаг для слоя |                                 |                                                                    |  |  |

|------------------------------|--------------------------------------|---------------------------------|--------------------------------------------------------------------|--|--|

| Layer                        | Routing-<br>Layers                   | Routing-<br>Layers_Diff         | Routing-<br>Layers_Power                                           |  |  |

|                              | All                                  | InAny-<br>Differential-<br>Pair | (InNetClass<br>('PowerGlobal')<br>Or InNetClass<br>('PowerLocal')) |  |  |

| 10_Top                       | +                                    | +                               |                                                                    |  |  |

| 9_underTop                   | +                                    |                                 |                                                                    |  |  |

| 7_Mid                        | +                                    |                                 | +                                                                  |  |  |

| 6_Mid_VCC                    |                                      |                                 | +                                                                  |  |  |

| 4_Mid                        | +                                    |                                 | +                                                                  |  |  |

| 2_OverBottom_<br>forDiffPair |                                      | +                               |                                                                    |  |  |

| 1_Bottom                     |                                      |                                 |                                                                    |  |  |

пей в нашем примере правилами, указанными в таблице 3.

#### Раздел правил Routing/Routing Corners

- 1. Имя правила RoutingCorners. Укажем стиль проводника при его повороте в одном слое, а именно разрешим при этом использовать «скос» под углом 45 градусов с заданным диапазоном длины «скоса»:

- Условие All.

- Параметры: Style=45 Degrees;

Setback=12 to 100 mil.

- 2. Имя правила RoutingCorners. Укажем стиль проводника при повороте для дифференциальных линий, а именно разрешим использовать «закругление»:

- Условие **All**.

- Параметры: Style=Rounded;

Setback=12 to 100 mil.

#### Раздел правил Routing/Routing Vias Style

В таблице 4 представлены правила этого раздела, начиная с низшего приоритета. Разнообразие переходных типов переходных отверстий вызвано максимальным соблюдением технологических параметров и обеспечением гарантированного соблюдения максимального тока через переходное отверстие в соответствии с рекомендациями стандартов IPC.

#### Раздел правил Routing/Fonout Control

Данный раздел правил рассмотрим позже, на примере выполнения операций **Fonout**.

#### Раздел правил

#### Routing/Differential Pours Routing

Здесь приведем только одно правило.

Имя правила — **DiffPairsRouting.** Здесь укажем зазор между двумя проводниками одной дифференциальной пары, при этом приведем их только для двух слоев: верхнего, где находятся компоненты, и слоя **2\_OverBottom\_forDiffPair**, предназначенного для прокладки проводников дифференциальной линии:

- Условие All.

- Параметры: Min Gap=5 mil для всех слоев, Preffered Gap=7,6 mil для слоя 2\_Over-Bottom\_forDiffPair и 8,5 mil для слоя 10\_TOP, Degrees; Max Gap=20 mil для всех слоев. Нижняя и верхняя границы выбраны для обеспечения подвода пары к PAD,

Таблица 4. Назначение параметров переходных отверстий для классов и типов

|                                                                                                 |                                                                                                                        | Параметры    |        |           |                |        |           |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------|--------|-----------|----------------|--------|-----------|

| Имя правила<br>(комментарий)                                                                    | <b>У</b> словие                                                                                                        | Via Diameter |        |           | Via Holes Size |        |           |

| (Rominorraphin)                                                                                 |                                                                                                                        | Min          | Max    | Preferred | Min            | Max    | Preferred |

| RoutingViasDefault (по умолчанию)                                                               | All                                                                                                                    | 18 mil       | 34 mil | 22 mil    | 6 mil          | 10 mil | 8 mil     |

| RoutingVias_Power (для проводников класса питающих напряжений)                                  | (InNetClass('PowerGlobal') Or InNetClass('PowerLocal'))                                                                | 21 mil       | 30 mil | 21 mil    | 12 mil         | 15 mil | 12 mil    |

| RoutingVias_PowerLoop<br>(для локальных силовых проводников<br>DC/DC- преобразователей)         | InNetClass('PowerLoop')                                                                                                | 21 mil       | 30 mil | 30 mil    | 12 mil         | 15 mil | 15 mil    |

| RoutingVias_nexttoBGA<br>(в зоне BGA-корпусов)                                                  | (TouchesRoom('A2') Or TouchesRoom('A4') Or TouchesRoom('A8'))                                                          | 14 mil       | 21 mil | 16 mil    | 6 mil          | 12 mil | 8 mil     |

| RoutingVias_nexttoBGA_Power<br>{в зоне BGA-корпусов<br>для силовых линий)                       | (InNetClass('PowerGlobal') Or InNetClass('PowerLocal')) And (WithinRoom('A2') Or WithinRoom('A4') Or WithinRoom('A8')) | 14 mil       | 30 mil | 21 mil    | 6 mil          | 15 mil | 12 mil    |

| RoutingVias_withinBGA<br>(для BGA-корпусов<br>при операции Fonout)                              | inBGA Or<br>((BigColumnCount >= 6)<br>And (BigRowCount >= 6))                                                          | 14 mil       | 21 mil | 14 mil    | 6 mil          | 12 mil | 6 mil     |

| RoutingVias_Heatsink_PAD<br>(для корпусов типа QFN, имеющих<br>специальный PAD для теплоотвода) | InPadClass('Heatsink_PAD')                                                                                             | 21 mil       | 30 mil | 35 mil    | 12 mil         | 15 mil | 15 mil    |

значение **Preffered Gap** — расчетное для этих слоев в соответствии с выбранным **Layer Stack**, как указано в [1, рис. 5].

На рис. 6, в частности, показано:

- а) ширина (6 mil) проводника дифференциальной линии на слое 2\_OverBottom\_ forDiffPair, которая соответствует нашему правилу 4 раздела Routing Widht;

- b) расстояние (13,6 mil) между центрами проводников дифференциальной линии.

Таким образом, зазор между проводниками составляет 13,6-6=7,6 mil в полном соответствии с только что определенным правилом.

#### Раздел правил SMT

- Имя правила SMDToCorner (подраздел SMD To Corner). Зададим минимальное расстояние до первого поворота проводника вблизи PAD:

- Условие Not InAnyDifferentialPair. Данное правило не будет распространяться на проводники дифференциальных линий.

- Параметры: Distance=4 mil.

- 2. Имя правила SMDNeckDown (подраздел SMD Neck-Down). Определяет способ подключения проводников к PAD.

- Условие **IsSMTPin**. Для данного типа контактных площадок.

- Параметры: Neck-Down=68%. Ширина подводящего проводника должна быть меньше ширины площадки на указанную величину.

- 3. Имя правила SMDNeckDown\_NetTie (подраздел SMD Neck-Down). Для специальных компонентов, которые физически замыкают разные электрические связи на печатной плате, выполнены топологически и не требуют монтажа, разрешим подвод и более широких проводников. Этот элемент и его подключение были показаны на рис. 5, сноска 3с. Как создавать и использовать такие элементы, описано в [2], однако мы еще раз укажем на особенности использования таких элементов:

- HOST.D

Рис. 6. Дифференциальная линия

- Условие IsSMTPin And InPadClass-('NetTie'). Указаны объекты правила: контактные площадки как элементов поверхностного монтажа, так и отнесенных к классу 'NetTie'.

- Параметры: Neck-Down=1000%. То есть ширина подводящего проводника может быть в 10 раз больше ширины самой контактной площадки.

#### Раздел правил Mask

Кроме правила по умолчанию с зазором 3 mil, для BGA-компонента с шагом 0,65 мм создадим дополнительное правило с меньшим зазором:

- Имя правила SMDToCorner.

- Условие IsPad And InComponent('U1')

для контактных площадок конкретного

компонента.

- Параметры: Expansion=2,1 mil.

#### Раздел правил Plane

В подразделе **Power Plane Connect Style** создадим следующие правила подключения к слоям типа Plane:

- 1. Имя правила **PlaneConnect** для подключения по умолчанию:

- Условие All.

- Параметры: Connect Style=Relief Connect, Conductor = 4, Conductor Widht = 7 mil, Air Gap = 3 mil, Expansion = 4 mil. Под-ключение типа термобарьер с четырьмя проводниками шириной 7 mil, шириной термозазора 3 mil и значением ширины (4 mil) пояска вокруг Hole.

- 2. Имя правила PlaneConnect\_BigPad для подключения к контактным площадкам большого размера, имеющим отверстия (Hole):

- Условие PadIsPlated And (PadXSize\_ AllLayers > 50) для всех металлизированных отверстий с диаметром больше 50 mil.

- Параметры: Connect Style = Relief Connect,

Conductor = 4, Conductor Widht = 12 mil,

Air Gap = 6 mil, Expansion = 20 mil. Все значения параметров подключения увеличены.

- 3. Имя правила PlaneConnect\_Via для подключения к переходным отверстиям:

- Условие IsVia.

- Параметры: Connect Style = Direct Connect.

Здесь не имеет смысла обеспечивать термобарьер, и переходные отверстия будут подключены к слою сплошной металлизацией.

- 4. Имя правила PlaneConnect\_BigHole для подключения к контактным площадкам, имеющим отверстия (Hole) с большим значением диаметра. Отметьте разницу с правилом 2, которое распространяется на контактные площадки с большим размером только на слое TOP, каковые могут иметь и небольшие отверстия.

- Условие (ObjectKind = 'Pad') And (HoleDiameter >= '50').

- Параметры: Connect Style = Relief Connect,

Conductor = 4, Conductor Widht = 12 mil,

Air Gap = 6 mil, Expansion = 20 mil. Все значения параметров увеличены.

В подразделе **Power Plane Clearance** зададим правила зазора к тем отверстиям, которые не имеют подключения к слою Plane.

- 5. Имя правила **PlaneClearance**. Это значения зазора по умолчанию:

- Условие All.

- Параметры: Clearance = 6 mil.

- 6. Имя правила PlaneClearance\_BGA для подключения в зоне BGA посадочных мест. В этой зоне печатной платы будут заданы наиболее жесткие требования по зазорам:

- Условие inBGA Or ((BigColumnCount >= 6) And (BigRowCount >= 6) And inSMT-Component).

- Параметры: Clearance = 3,6 mil. В подразделе Polygon Connect Style зададим правила подключения к полигонам.

- Имя правила PolygonConnect. Подключение к полигону по умолчанию:

- Первое условие All.

- Второе условие All.

- Параметры: Connect Style = Relief Connect, Conductor = 4. 45 Angle, Conductor Widht = 5 mil. Заметим, что в отличие от подключения к слоям типа Plane здесь есть возможность выбора угла подключения проводников, однако отсутствует параметр Air Gap (задание зазора сделано в разделе правил Electrical/Clearance) и Expansion (значения размеров контактных площадок и диаметра переходных отверстий определяются непосредственно в их свойствах).

- Имя правила PolygonConnect\_TOPand-BOTforVia. Способ подключения переходных отверстий к полигону на внешних сторонах печатной платы:

- Первое условие OnOutside.

- Второе условие IsVia.

- Параметры: Connect Style = Relief Connect,

Conductor = 4. 45 Angle, Conductor Widht = 4 mil.

- 9. Имя правила PolygonConnect\_TOPand-BOTforPAD. Способ подключения контактных площадок к полигону на внешних сторонах печатной платы. Использование Relief Connect при подключении к полигону может вызвать неравные условия при монтаже из-за разного термопрофиля для идентичных контактных площадок. Это правило запрещает такое подключение:

- Первое условие OnOutside.

- Второе условие **IsPad**.

- Параметры: Connect Style = No Connect.

- Имя правила PolygonConnect\_to\_Via.

Способ подключения полигона к переходным отверстиям на внешних слоях:

- Первое условие OnOutside.

- Второе условие **IsVia**.

- Параметры: Connect Style = Direct Connect.

Переходные отверстия будут подключены к полигону сплошной металлизацией.

#### Продолжение следует

#### Литература

- 1. Пранович В. Altium Designer (build 7.x). Проект многослойной печатной платы // Технологии в электронной промышленности. 2008. № 6.

- Пранович В. Система проектирования Altium Designer 6 // Технологии в электронной промышленности. 2007. № 1.