- Mixed VHDL / Verling Simulation

- Co-Simulation for C/C++ and SystemC<sup>™</sup>

- Advanced Design Debugging

- Assertion-based Verification

- Hardware Acceleration

Система моделирования Riviera является последним решением для высокопроизводительной верификации проектов интегральных схем. Применение подхода «лучший в своем классе» дало наиболее гибкую платформу для VDHL, Verilog и смешанного моделирования. Система Riviera идеально подходит для отладки проектов на уровне регистровых передач, длительного регрессивного тестирования, временного моделирования, методологий групповой разработки и включает в себя непосредственную связь с аппаратным ускорителем посредством Riviera-IPT.

#### МОДЕЛИРОВАНИЕ НА СМЕШАННЫХ ЯЗЫКАХ

Система Riviera поддерживает разработку наиболее сложных проектов интегральных схем, состоящих из проектных блоков на языках VHDL, Verilog, C/C++, SystemC и списков цепей в формате EDIF, обеспечивая их полную интеграцию на основе общего ядра моделирования.

# **СОВМЕСТНОЕ МОДЕЛИРОВАНИЕ С С/С++ И SYSTEMC**

Новые методы проектирования продолжают вести к сокращению времени верификации. Система Riviera включает в себя возможность совместного моделирования тестов и проектных модулей C/C++ и SystemC вместе с модулями VHDL и Verilog. Система моделирования непосредственно соединяется с компилятором C, а комбинированные результаты моделирования могут просматриваться в редакторе временных диаграмм.

### РЕЖИМЫ ОПТИМИЗАЦИИ МОДЕЛИРОВАНИЯ

Система Riviera может быть сконфигурирована для оптимизации моделирования и повышения производительности как в графическом, так и в фоновом режиме моделирования. Средства управления производительностью включают в себя:

- Оптимизированный режим компиляция и моделирование проектов на языке Verilog и смешанных VHDL/Verilog проектов вместе в тестами.

- Управление разбросом памяти распределение под проект только памяти, требуемой в процессе верификации.

- Управление выключенными блоками маскирование блоков проекта, которые не контролируются во время моделирования.

### ВЕРИФИКАЦИЯ НА ОСНОВЕ УТВЕРЖДЕНИЙ

Использование верификации на основе утверждений является ценным дополнением в процессе проектирования, интеграции, моделирования системы и передачи проекта на изготовление, обеспечивая лучшее (внутреннее) понимание функционирования проекта. Утверждения ускоряют процесс отладки, сокращая количество итераций верификации, улучшают возможности повторного использования проекта и передачи его контрагентам, и могут также использоваться в аппаратном ускорителе (Riviera-IPT). Поддержка стандартов верификации на основе утверждений включает в себя:

- Утверждения OpenVera (OVA)

- Язык определенных свойств (PSL)

- Библиотеки открытой верификации (OVL)

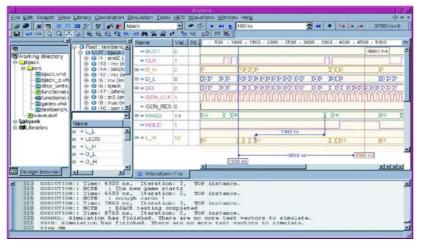

# ВЫСОКОПРОИЗВОДИТЕЛЬНЫЙ РЕДАКТОР ВРЕМЕННЫХ ДИАГРАММ

Редактор временных диаграмм использует несколько методов компрессии для обработки большого объема данных моделирования и ускорения визуализации временных диаграмм. Помимо высокой производительности, редактор также включает в себя несколько функций, которые упрощают верификацию проектов, позволяя производить более быстрое и точное редактирование и анализ

результатов моделирования. Функции редактирования включают в себя возможность модификации значений и цепей, которые затем могут быть применены к последующим прогонам моделирования. Дополнительные функции включают в себя:

- Поддержку форматов VCD и расширенный VCD

- Показ источников событий

- Сравнение временных диаграмм

- Управление стимулятором

- Просмотр списков (.lst)

# ИНТЕРФЕЙСЫ ІЕЕЕ

Система моделирования Riviera включает в себя интерфейсы PLI, VPI и VHPI, которые являются стандартами IEEE, для связи с другими средствами верификации в маршруте проектирования. В дополнение к стандартным интерфейсам, Riviera также включает в себя оптимизированную интеграцию с отдельными средствами проектирования стратегических партнеров компании Aldec.

### ПОДДЕРЖКА МНОГОМАШИННЫХ СЕРВЕРНЫХ СИСТЕМ

Система Riviera совместима со всеми методологиями управления загрузкой многомашинных серверных систем, конфигурируемых для операционных систем UNIX, Linux или NT. Проекты могут быть перегружены для моделирования с локальной рабочей станции или персонального компьютера в централизованное место, высвобождая локальный компьютер для работы с другими частями проекта.

#### КОДИРОВАНИЕ БИБЛИОТЕК

Система Riviera предоставляет средства компрессии и кодирования исходных кодов на языках VHDL и Verilog для безопасной упаковки и обмена проектными модулями между членами рабочей группы локально или по сети.

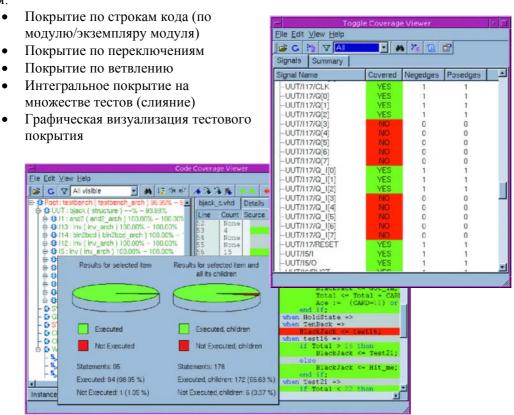

### ТЕСТОВОЕ ПОКРЫТИЕ

Анализ тестового покрытия обычно дает большую нагрузку на системы моделирования и замедляет сам процесс моделирования. Поскольку эта функция встроена непосредственно в систему Riviera, связанные с этим накладные расходы значительно сокращаются. Тестовое покрытие в системе Riviera включает в себя:

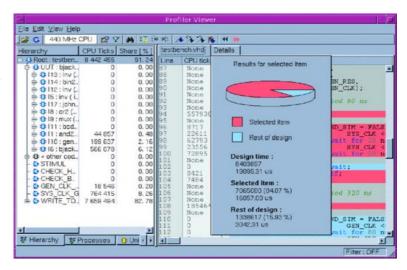

#### ПРОФИЛИРОВАНИЕ ПРОЕКТА

Проектные блоки, занимающие большое время моделирования, могут быть легко определены с помощью функции профилирования проекта. За счет идентификации этих блоков и оптимизации тех частей проекта, которые увеличивают время моделирования, общее время моделирования проекта может быть существенно уменьшено. Моделирование может быть очень неэффективным без возможности увидеть характеристики проекта и установить деградацию моделирования.

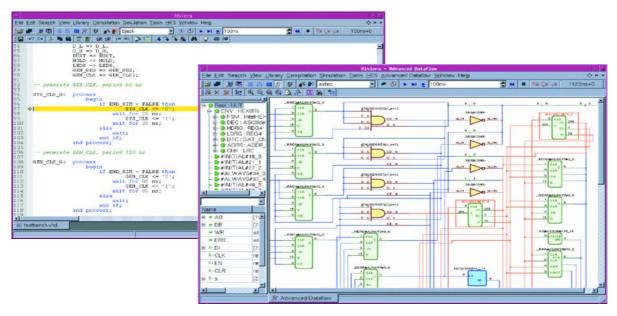

### МОЩНЫЙ РЕДАКТОР

Текстовый редактор языков описания аппаратуры высокого уровня интегрирован с компилятором и ядром моделирования для облегчения отладки, позволяя делать установку точек останова и быструю локализацию ошибок компиляции.

### АППАРАТНОЕ УСКОРЕНИЕ RIVIERA-IPT

Система Riviera может быть расширена дополнительным патентованным аппаратным ускорителем Riviera-IPT, который обеспечивает большую скорость и эффективность моделирования за счет соединения вместе многих различных элементов проектирования и верификации в единую ускорительную платформу системного уровня. Эта платформа соединяет в себе программное моделирование для смешанных описаний VHDL, Verilog, утверждений, совместное моделирование с кодом C/C++, SystemC и аппаратное ускорение, все оптимизированные и включенные в архитектуру общего ядра. Ключевые особенности включают в себя:

- Ускорение моделирования кода на уровне регистровых передач в 10-50 раз

- Не требуется длительного обучения или выполнения предварительных установок

- Поддержка сетевых и групповых режимов работы

- Масштабируемая архитектура

- Высшее качество проектирования

- Поддержка методологии многомашинных серверных систем

#### МЕТОДОЛОГИЯ RIVIERA-IPT

Традиционные методологии моделирования требуют от пользователя повторного моделирования ранее проверенных блоков с добавлением каждого нового блока или с каждой новой итерацией проекта, делая процесс верификации медленным и неэффективным. Однако, так как технология дифференциального создания прототипа (Incremental Prototyping Technology - IPT) предусматривает вывод всех отверифицированных блоков в аппаратуру, Riviera-IPT программно моделирует только вновь добавляемые блоки, существенно ускоряя процесс моделирования.

#### ТЕХНИЧЕСКАЯ ПОДДЕРЖКА

Компания Aldec предоставляет наивысший уровень сопровождения пользователей в промышленности. Годовая поддержка включает в себя неограниченную техническую поддержку по всему миру, ежеквартальные поставки новых версий программного продукта и его обновлений, подписку на наш информационный бюллетень и конференции, включая доступ в режиме онлайн к нашей библиотеке технической поддержки.

#### РАСШИРЕННЫЕ СРЕДСТВА ОТЛАДКИ

Система Riviera дает возможность редактирования и отладки VHDL, Verilog и смешанных проектов, выполнение отладки исходного кода в режиме онлайн или после моделирования с использованием нескольких расширенных функций, которые предоставляют разработчикам полный контроль над исходным кодом и ускоряют процесс отладки проектов.

#### ПРОВОДНИК СИГНАЛОВ (Только для VHDL)

Проводник сигналов позволяет разработчику контролировать и запускать сигналы из любого блока VHDL. При этом не требуется, чтобы сигналы были разведены через интерфейсы блоков или объявлены в глобальных пакетах. Это особенно полезно при разработке тестов и верификации проектов.

## ПРОСМОТР СОСТОЯНИЙ ПАМЯТИ

Система Riviera упрощает процесс отладки, показывая содержимое памятей, определенных в проекте, как для VHDL, так и для Verilog описаний. Запоминаемые значения могут наблюдаться во время моделирования в окне графической визуализации памяти.

#### Х-ТРАССИРОВКА

X-трассировка позволяет разработчику отслеживать и просматривать события, вызывающие неожидаемые выходные значения во время моделирования. Обращение к этой функции выполняется через окно анализа потока данных в соединении с редактором временных диаграмм. Использование X-трассировки существенно сокращает общее время отладки.

### ПРОГРЕССИВНЫЙ ПОТОК ДАННЫХ

Эта функция дает возможность просмотра и отладки проекта в графическом виде и полезна для исследования его физической связанности в виде блок-диаграмм как для VHDL, так и для Verilog описаний. Она непосредственно связана с автономным редактором временных диаграмм Riviera и позволяет использовать курсор для прокрутки временой шкалы моделирования вперед и назад для наблюдения в это время аннотированных значений сигналов на блок-диаграмме.

### ОПЕРАЦИОННЫЕ СИСТЕМЫ

- Sun Solaris (7, 8 и 9)

- Linux (ядро 2.4)

- Windows NT/2000/XP

#### СИСТЕМНЫЕ ТРЕБОВАНИЯ

- Компьютер, совместимый со Sparc или Pentium PC

- 256Мбайт физической памяти, рекомендуется 512Мбайт

- 100 Мбайт свободного дискового пространства (для полной инсталляции)

### ПОДДЕРЖИВАЕМЫЕ СТАНДАРТЫ

- VHDL 1076-87/93

- Verilog 1364-95/2001

- VITAL 1076.4-95/2000

- SDF 1.0, 2.0 и 3.0

- SystemVerilog

### Интерфейсы

- Tcl/Tk

- PERL

- PLI/VPI

- VHPI

- CHPI

# ФУНКЦИОНАЛЬНЫЕ ХАРАКТЕРИСТИКИ

| Моделирование                  |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Смешанное моделирование        | Общее ядро моделирования для VHDL, Verilog и EDIF                         |

| Моделирование в фоновом режиме | Запуск моделирования из системной оболочки без графического интерфейса    |

| Управление разбросом памяти    | Уменьшение требований к системной памяти во время моделирования           |

| Случайные стимулы              | Генерация случайных тестовых воздействий для моделей                      |

| Оптимизация Vital              | Повышение производительности со встроенными моделями и библиотеками Vital |

| VCD и расширенный VCD          | Поддержка файлов в форматах VCD и расширенный VCD                         |

| Кодирование и компрессия       | Сжатие и защита ІР-блоков для обмена в рабочих группах                    |

| Расширенная отладка          |                                                                               |

|------------------------------|-------------------------------------------------------------------------------|

| Поддержка утверждений        | Спецификация проекта для выражения системных ограничений                      |

| Отладка исходного кода       | Пошаговое выполнение, установка точек останова в коде                         |

| Точки останова для сигналов  | Установка точек останова на события, транзакции или значения                  |

| Прогрессивный поток данных   | Графическое представление сигналов/цепей для процессов во время моделирования |

| Х-трассировка                | Отслеживание и просмотр событий, вызывающих неожидаемые выходные сигналы      |

|                              | во время моделирования                                                        |

| Редактор временных диаграмм  | Просмотр результатов в прцессе моделирования или загрузка диаграмм из файлов  |

| Сравнение временных диаграмм | Автоматическое сравнение двух временных диаграмм и выделение различий         |

| Просмотр источников событий  | Прямое позиционирование на оператор HDL, вызывающий событие                   |

| Проводник сигналов           | Контроль и управление сигналами VHDL и Verilog в любом месте иерархии проекта |

| Просмотр состояний памяти    | Просмотр состояний больших массивов памяти                                    |

| Тестовое покрытие         |                                                                        |

|---------------------------|------------------------------------------------------------------------|

| Покрытие по строкам кода  | Покрытие по каждому модулю или экземпляру модуля в исходном коде       |

| Слияние тестов            | Слияние результатов по нескольким прогонам моделирования               |

| Покрытие по переключениям | Измерение активности проекта по изменению логических значений сигналов |

| Анализ тестового покрытия | Сохранение данных и их анализ в автономном                             |

| Пользовательский интерфейс |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Броузер проекта            | Интерактивный интерфейс управления библиотеками, моделированием и отладкой |

| Профилирование проекта     | Показывает число тактов процессора для каждого исполняемого оператора      |

| Структура проекта          | Анализ структуры проекта, просмотр сигналов, портов и переменных           |

| Редактор языков            | Редактирование кода HDL, продвижение по коду во время моделирования        |

| Управление библиотеками    | Просмотр содержимого и назначения библиотек                                |

| Регенерация библиотек      | Обновление библиотек без перекомпиляции при переходе на новые версии       |

| Окно списков               | Просмотр результатов в формате списков; сохранение в файлы списков         |

| Внешние интерфейсы           |                                                                                                                |

|------------------------------|----------------------------------------------------------------------------------------------------------------|

| Интерфейс VHPI               | Стандартный интерфейс для доступа к моделям VHDL при моделировании                                             |

| Verilog PLI и VPI            | Стандартный интерфейс IEEE для доступа к моделям Verilog при моделировании                                     |

| Novas – Debussy              | Интерактивный или фоновый режимы для новой структуры базы данных FSDB                                          |

| Verisity - Specman           | Прямой интерфейс в графическом и фоновом режимах для построения тестов с                                       |

| verisity specimen            | использованием языка «е»                                                                                       |

| Denali – SOMA                | Интерфейс PLI к моделям быстрой памяти для VHDL и Verilog                                                      |

| Cadence - Testbuilder        | Доступ к тестовым библиотекам С/С++ через интерфейс СНРІ высокого уровня                                       |

| Summit Design – Visual Elite | Интерактивная спецификация проекта и отладка через интерфейсы API, VHPI и PLI                                  |

| Synopsys - SWIFT             | Подстановка скомпилированных поведенческих моделей в проект HDL; Включает расширения MemPro, DesignWare и LMTV |

| SystemC                      | Совместное моделирование SystemC c VHDL/Verilog                                                                |

| Аппаратное ускорение |                                                                      |

|----------------------|----------------------------------------------------------------------|

| IPTv2000             | Аппаратный ускоритель Riviera-IPT емкостью 2 миллиона вентилей ПЛИС  |

| IPTv6000             | Аппаратный ускоритель Riviera-IPT емкостью 6 миллиона вентилей ПЛИС  |

| IPTv12000            | Аппаратный ускоритель Riviera-IPT емкостью 12 миллиона вентилей ПЛИС |

ООО "ЕвроИнТех" 109387, Россия, Москва,

ул. Летняя, д. 6

Телефон/факс: +7-(495)-749-45-78

E-mail: sales@eurointech.ru http://www.eurointech.ru