## Продукты компании Aldec для проектирования цифровых устройств

В начале 2004 года компания Aldec (www.aldec.com) обновила свою линейку продуктов для проектирования цифровых устройств Active-HDL и Riviera.

истема проектирования Active-HDL 6.2 является на сегодня ведущей средой проектирования для создания и моделирования проектов всех семейств ПЛИС, обеспечивающей гибкость подхода и предоставляющей развитые функции поддержки наиболее сложным современным проектам. Среда проектирования Active-HDL даёт разработчикам независимость в использовании средств проектирования из единого, полностью интегрированного окружения. Тесная интеграция всех приложений даёт возможность абсолютного контроля над проектом от спецификации на всём пути к его физической реализации. Программа Active-HDL также имеет интерфейсы со всеми ведущими программными продуктами и предоставляет разработчикам свободу в использовании тех средств проектирования, которые наиболее полно отвечают требованиям каждого конкретного проекта.

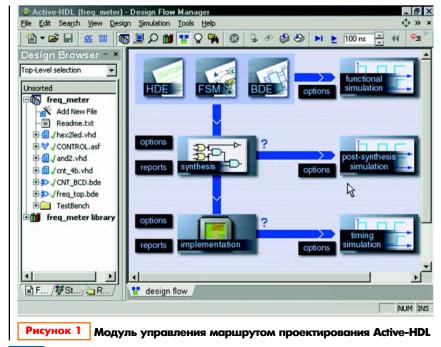

Система Active-HDL структурно построена вокруг блока управления маршрутом проектирования, который даёт возможность пользователям легко полу-

чать доступ к используемым средствам проектирования и библиотекам (рис. 1). Программа поставляется с обширным набором библиотек ведущих производителей ПЛИС, включающих прекомпилированые и готовые к использованию компоненты. Блок управления проектом Active-HDL позволяет разработчику выполнять все модификации и операции над проектом из единого окружения, что обеспечивает лучший контроль над процессом проектирования и сокращает временные затраты, устраняя необходимость в запуске множества оконных интерфейсов и процессов.

Маршрут проектирования компании Aldec не зависит от производителя ПЛИС и настраивается на любые комбинации средств логического синтеза и топологической реализации ПЛИС. Разработчик цифровых систем может делать проекты на ПЛИС любого производителя из единой интегрированной среды.

Разработчики могут одновременно открывать несколько проектов и интег-

рировать их в один суперпроект. Мультипроектная рабочая область предоставляет среду проектирования, позволяющую пользователям управлять всеми загруженными проектами, переключаться с одного на другой, редактировать их ресурсы и конфигурировать их независимо друг от друга. Все модули могут разрабатываться отдельно друг от друга и затем интегрироваться вместе как один проект верхнего уровня.

Увеличение размеров проектов вынуждает многих разработчиков ПЛИС использовать методы групповой разработки при проектировании. Программа Active-HDL предоставляет средства повышения производительности, например, такие, как модуль управления заданиями для задач, занимающих много времени на выполнение (моделирование, логический синтез, топологическая реализация). Каждая задача может быть назначена на удалённый сервер или кластер других компьютеров для выполнения соответствующего задания, таким образом, высвобождая компьютер разработчика для других целей. Система Active-HDL также предоставляет интерфейс к более чем 15 наиболее популярным системам управления версиями (RCS).

Система управления проектами обеспечивает быстрое и эффективное управление всеми ресурсами проектов. Разработчики могут использовать её для:

- добавления, удаления, просмотра, модификации или выполнения других операций над файлами ресурсов проекта;

- просмотра содержимого рабочей библиотеки, библиотеки результатов логического синтеза и библиотеки временных параметров текущего проекта;

- просмотра сконструированной структуры моделируемого проектного модуля;

- просмотра объектов, определённых внутри отдельных областей моделируемого проектного модуля.

Система управления библиотеками предоставляет эффективное управление всеми библиотеками в среде проектирования Active-HDL. Пользователи могут выполнять следующие операции над библиотеками и их содержимым:

- присоединение, отсоединение и удаление библиотек;

- редактирование логических имён библиотек;

- сжатие и освобождение библиотек;

- просмотр содержимого библиотек;

- просмотр исходных файлов определённых библиотечных модулей;

- удаление определённых библиотечных модулей;

- поиск проектных модулей в библиотеках.

Разработчики цифровых систем имеют доступ к наиболее полно протестированным и проверенным в промышленности IP-блокам. Они могут использовать встроенный генератор IP-блоков для создания требуемых моделей, таких как арифметические функции, последовательностная логика, блоки памяти, фильтры, конверторы кодов, элементы для построения тестов, промышленные и коммуникационные приложения.

Трассировка всех сигналов даёт возможность разработчикам выполнять кросс-отладку (зондирование) между временными диаграммами и блок-диаграммами. Такая трассировка позволяет сделать обратную аннотацию проекта и даёт прямой доступ как к текстовому, так и графическому представлению проекта. Щелчок мышью на любом сообщении об ошибке или предупреждающем сообщении адресует разработчика непосредственно на соответствующую строку исходного кода.

Средства анализа тестового покрытия идентифицируют те части проекта, которые не исполнялись во время прогона теста, и дают возможность инженеру легко определить, какие части теста требуют доработки. Все средства интегрированы в ядро моделирования и поддерживают функции покрытия по строкам кода, по переключениям и интегральное покрытие на множестве тестов.

Система Active-HDL предоставляет интерфейс и возможность совместного моделирования поведенческих моделей на языках описания аппаратуры и блоков цифровой обработки сигналов в единой среде математического представления моделей высокого уровня.

Прямой интерфейс с системой Simulink компании Mathworks автоматизирует процесс установки для выполнения совместного моделирования с Active-HDL.

Проекты, сделанные в среде Active-HDL, могут быть экспортированы во внешний файл формата HTML. Такой файл HTML поддерживает ту же самую структуру и иерархию проекта, что и Active-HDL, без необходимости работы с самой системой моделирования. В итоге проекты могут без труда разделяться среди членов рабочей группы и идеальны для документирования.

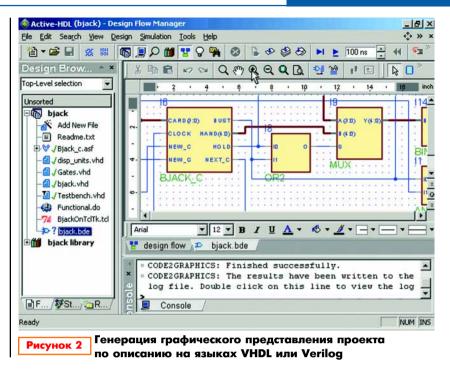

Функция Code2Graphics может генерировать графическое представление проектов, сделанных на языках VHDL или Verilog (рис. 2). Эта функция даёт разработчикам систем ясную картину взаимосвязей между компонентами, используемыми в проекте. Она анализирует исходные файлы на языках VHDL, Verilog или в формате EDIF и генерирует один или более файлов блок-диаграмм, в зависимости от количества проектных объектов, модулей или элементов, найденных в анализируемых файлах. Результирующие графические файлы (блокдиаграммы или диаграммы автоматов конечных состояний) могут быть автоматически присоединены к проекту или размещены отдельно.

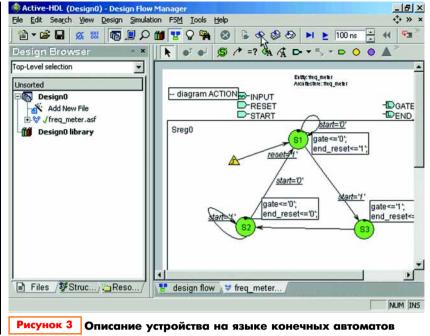

Система Active-HDL может использоваться для автоматической генерации тестов из графических временных диаграмм или диаграмм автоматов конечных состояний (рис. 3). Генератор тес-

тов руководит последовательностью действий инженера в диалоговом режиме и создаёт шаблон теста либо для отдельного процесса, либо на основе IEEE Waves. Один и тот же тест может использоваться на любом уровне абстракций в процессе проектирования (поведенческом, регистровых передач или временном).

Проектные блоки, занимающие большое время моделирования, могут быть легко определены с помощью функции профилирования проекта. За счёт идентификации этих блоков и оптимизации тех частей проекта, которые увеличивают время моделирования, общее время моделирования проекта может быть существенно уменьшено. Моделирование может быть очень неэффективным без возможности увидеть характеристики проекта и установить деградацию моделирования.

Система Active-HDL полностью совместима с системой моделирования Riviera компании Aldec. Использование системы Riviera даёт возможность Active-HDL производить моделирование в среде многомашинных серверных систем и на других поддерживаемых платформах операционных систем, включая Linux и Unix

Система моделирования Riviera является последним решением для высокопроизводительной верификации проектов интегральных схем. Применение подхода "лучший в своём классе" дало наиболее гибкую платформу для VDHL,

Verilog и смешанного моделирования. Система Riviera идеально подходит для отладки проектов на уровне регистровых передач, длительного регрессивного тестирования, временного моделирования, методологий групповой разработки и включает в себя непосредственную связь с аппаратным ускорителем посредством Riviera-IPT.

Система Riviera поддерживает разработку наиболее сложных проектов интегральных схем, состоящих из проектных блоков на языках VHDL, Verilog, C/C++, SystemC и списков цепей в формате EDIF, обеспечивая их полную интеграцию на основе общего ядра моделирования.

Новые методы проектирования позволяют сократить время верификации. Система Riviera даёт возможность совместного моделирования тестов и проектных модулей С/С++ и SystemC вместе с модулями VHDL и Verilog. Система моделирования непосредственно соединяется с компилятором С, а комбинированные результаты моделирования могут просматриваться в редакторе временных диаграмм.

Система Riviera может быть сконфигурирована для оптимизации моделирования и повышения производительности как в графическом, так и в фоновом режиме моделирования. Средства управления производительностью включают в себя:

- оптимизированный режим компиляция и моделирование проектов на языке Verilog и смешанных VHDL/ Verilog-проектов вместе в тестами;

- управление разбросом памяти выделение под проект такого количества памяти, которое требуется в процессе верификации;

- управление выключенными блоками маскирование блоков проекта, которые не контролируются во время моделирования.

Использование верификации на основе утверждений в процессе проектирования, интеграции, моделирования системы и передачи проекта на изготовление, обеспечивает лучшее (внутреннее) понимание функционирования проекта. Утверждения ускоряют процесс отладки, сокращая количество итераций верификации, улучшают возможности повторного использования проекта и передачи его контрагентам, и могут также применяться в аппаратном ускорителе (Riviera-IPT). Поддержка стандартов верификации на основе утверждений включает в себя утверждения OpenVera (OVA), язык определённых свойств (PSL), библиотеки открытой верификации (OVL).

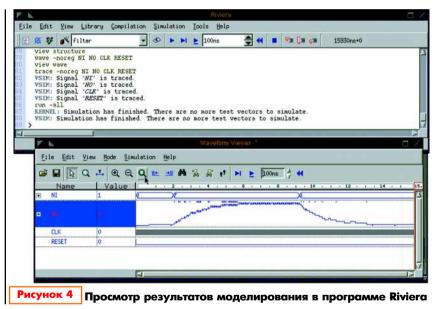

Редактор временных диаграмм использует несколько методов компрессии для обработки большого объёма данных моделирования и ускорения визуализации временных диаграмм. Помимо высокой производительности, редактор также включает в себя несколько функций, которые упрощают верификацию проектов, позволяя производить более быстрое и точное редактирования (рис. 4). Функции редактирования дают возможность модификации значений и цепей, которые затем могут быть применены к последующим прогонам моделирования.

Дополнительные функции предполагают поддержку простого и расширенного форматов VCD, показ источников событий, сравнение временных диаграмм, управление программой моделирования, просмотр списков (.lst).

Система моделирования Riviera включает в себя интерфейсы PLI, VPI и VHPI, которые являются стандартами IEEE, для связи с другими средствами верификации в маршруте проектирования. В дополнение к стандартным интерфейсам, Riviera также включает в себя оптимизированную интеграцию с отдельными средствами проектирования стратегических партнёров компании Aldec.

Система Riviera совместима со всеми методологиями управления загрузкой многомашинных серверных систем, конфигурируемых для операционных систем UNIX, Linux или NT. Проекты могут быть перегружены для моделирования с локальной рабочей станции или персонального компьютера в централизованное место, высвобождая локальный компьютер для работы с другими частями проекта.

Система Riviera предоставляет средства компрессии и кодирования исходных кодов на языках VHDL и Verilog для безопасной упаковки и обмена проектными модулями между членами рабочей группы локально или по сети.

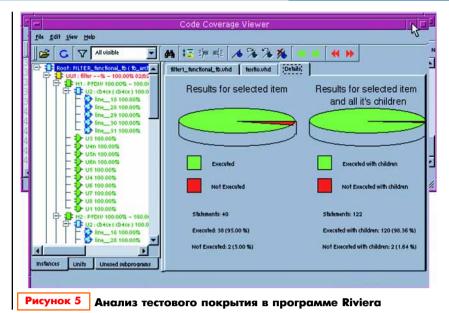

Анализ тестового покрытия обычно дает большую нагрузку на системы моделирования и замедляет сам процесс моделирования. Поскольку эта функция встроена непосредственно в систему Riviera, связанные с этим накладные расходы значительно сокращаются (рис. 5). Тестовое покрытие в системе Riviera включает в себя:

- покрытие по строкам кода (по модулю/экземпляру модуля);

- покрытие по переключениям;

- покрытие по ветвлению;

- интегральное покрытие на множестве тестов (слияние);

- графическая визуализация тестового покрытия.

Текстовый редактор языков описания аппаратуры высокого уровня интегрирован с компилятором и ядром моделирования для облегчения отладки, позволяя устанавливать точки останова и быстро локализовать ошибки компиляции.

Система Riviera может быть расширена дополнительным патентованным

аппаратным ускорителем Riviera-IPT, который обеспечивает большую скорость и эффективность моделирования за счёт соединения различных элементов проектирования и верификации в единую ускорительную платформу системного уровня. Эта платформа соединяет в себе программное моделирование для смешанных описаний VHDL, Verilog, утверждений, совместное моделирование с кодом C/C++, SystemC и аппаратное ускорение, все оптимизированные и включенные в архитектуру общего ядра.

Традиционные методологии моделирования требуют от пользователя повторного моделирования ранее проверенных блоков при добавлении каждого нового блока или при каждой новой итерации проекта, что делает процесс верификации медленным и неэффективным. Однако, так как технология диффе

ренциального создания прототипа (Incremental Prototyping Technology, IPT) предусматривает вывод всех проверенных блоков в аппаратуру, Riviera-IPT программно моделирует только вновь добавляемые блоки, существенно ускоряя процесс моделирования.

Программное обеспечение Aldec поддерживает следующие стандарты: VHDL 1076-87/93, Verilog 1364-95/2001 (частично), VITAL 1076.4-95/2000, SDF 1.0, 2.0 и 3.0.

Любую дополнительную информацию о продуктах компании Aldec можно получить в офисе компании ЭлекТрейд-М по телефону (095) 974-1480 или адресу info@eltm.ru.

По материалам компании Aldec