# Особенности технологии

# проектирования и производства LTCC-модулей

В статье рассматривается ряд общих проблем, возникающих при проектировании LTCC-устройств. Большое внимание уделяется выбору правильной методики моделирования как отдельных элементов, так и законченных LTCC-модулей.

#### Юрий Потапов

potapoff@eurointech.ru

ехнология низкотемпературной керамики (LTCC, Low Temperature Co-fired Ceramics) в настоящее время быстро развивается и успешно применяется для различных приложений, например, для производства ВЧ- и СВЧ-микросхем низкой и средней степени интеграции. В относительно низкой частотной области на базе LTCC-подложек изготавливаются устройства для GSM, CDMA, TDMA и Bluetooth приложений, а в области миллиметровых волн популярными становятся MMDS- и LMDSприложения. Данная технология обеспечивает недорогое решение в массовом производстве электронных устройств для коммерческой и военной областей электронной промышленности. И хотя использование LTCC-подложек позволило увеличить степень интеграции и снизить массо-габаритные параметры, для разработчиков оно породило целый ряд новых

Совместные усилия производителей систем САПР и разработчиков LTCC-устройств долгое время направлены на поиск наиболее эффективной методологии проектирования компактных модулей с ис-

пользованием высокочастотных систем моделирования. Главная проблема заключается в том, что LTCC-устройства имеют ярко выраженную трехмерную структуру; интегрированные компоненты и проводники здесь располагаются ближе друг к другу, поэтому хорошо зарекомендовавшие себя методики проектирования топологий печатных плат и интегральных схем не совсем подходят для их разработки. В данной статье мы детально рассмотрим процесс производства LTCC-устройств и обсудим некоторые проблемы разработчиков.

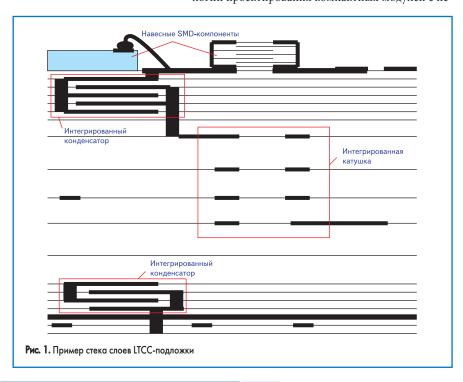

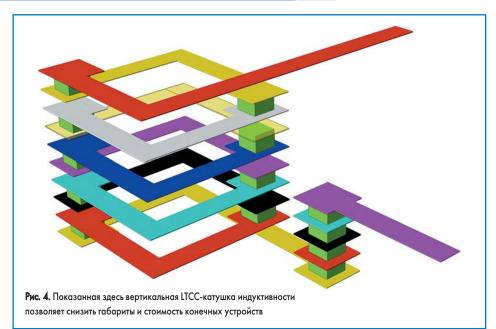

Типичный модуль, выполненный по технологии низкотемпературной спеченной керамики (LTCC), представляет из себя бутерброд из нескольких слоев керамического материала, запекаемый в печи обжига для фиксации многослойной структуры. Отличие от типичных многослойных печатных плат на основе фторопласта или высокотемпературной керамики, где каждый слой уже имеет проводящий рисунок и полностью подготовлен к прессовке, в LTCC-технологии проводящие чернила, формирующие рисунок топологии, наносятся на листы сырой керамики еще до операции спекания. Далее в слоях перфорируются отверстия, которые заполняются токопроводящей пастой, обеспечивающей электрическую связь между слоями и теплоотвод. В общем случае каждый отдельный слой в стеке LTCC-подложки может иметь уникальную толщину и диэлектрические характеристики, что дает разработчику широкие возможности реализации каждого многослойного компонента. Иными словами, если в какой-то части топологии необходимо сформировать специфический элемент, то принципиальных ограничений здесь не возникает. Например, стек, состоящий из шести тонких слоев с высоким значением относительной диэлектрической проницаемости Er, далее шесть толстых слоев с низким значением Ег и опять шесть тонких слоев с высоким значением Ег, позволяет на средней (внутренней) группе слоев реализовать вертикальную катушку индуктивности. Благодаря использованию расположенной в середине стека группы слоев с малым значением диэлектрической проницаемости можно снизить межвитковую емкость и повысить частоту первого собственного резонанса катушки. Верхние же группы тонких слоев позволяют организовать параллельные пластины многослойного конденсатора.

#### Технологии в электронной промышленности, № 3*′*2008

Рис. 2. Пример топологии тонкопленочного резистора

Один из примеров подобного стека слоев показан на рис. 1. Здесь тонкие слои имеют Er=20 и толщину 50 мкм. В середине подложки находятся шесть слоев толщиной 120 мкм с Er=8. На разрезе показаны спиральная катушка, два многослойных конденсатора, а также два внешних навесных элемента.

**Технология** производства LTCC-устройств выглядит следующим образом. Сырая керамика раскатывается, формуется и разрезается на листы фиксированного размера. Далее отбирается необходимое количество листов заданной толщины с требуемым значением диэлектрической проницаемости. В листах пробивается необходимое количество отверстий для межслойных проводящих и теплопроводящих переходов, а также выполняется дополнительная механическая обработка листов, например, краям придается специальная форма согласно конструкции изделия. Далее отверстия заполняются специальным проводящим составом, а на поверхность наносится проводящий рисунок топологии.

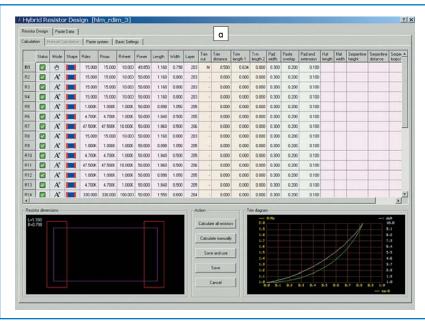

После этого выполняется сборка многослойной структуры подложки с тщательным совмещением многослойных переходных отверстий, причем в качестве связующего слоя используется закристаллизированное стекло. Затем на верхний и нижний слои наносится защитный слой и вся структура подвергается термообработке, в результате которой происходит ее спекание. После этого производится механическая обработка наружных слоев структуры (шлифование), в ходе которой снимается защитное покрытие, а сама поверхность становится плоской. Далее на очищенную поверхность верхнего и нижнего слоев наносится проводящий рисунок, а также резистивные элементы, причем для резисторов больших и малых сопротивлений используются разные резистивные чернила, с соответствующим удельным сопротивлением. Некоторые программные продукты предлагают специализированные средства разработки гибридных и тонкопленочных резисторов. Например, на рис. 2 показано окно модуля Hybrid Resistor Design пакета HYDE немецкой фирмы Durst

(www.durst.de) и пример разработанной топологии. После финального обжига наружных слоев выполняется лазерная подгонка номиналов резисторов, и подложка становится полностью подготовленной для поверхностного монтажа навесных компонентов.

В качестве навесных элементов на LTCC-подложках могут использоваться самые разнообразные компоненты для поверхностного монтажа, а это определяет широкий набор самих технологий монтажа. Кристаллы могут монтироваться на шариковые выводы или развариваться, перевернутые или обычные SMDустройства с выводами из никеля или палладия устанавливаются на паяльную пасту. Широкий набор технологий монтажа накладывает особые требования на последовательность сборки и отмывки подложек. Несмотря на то, что в общем случае в LTCC-модуле может быть применена абсолютно произвольная конфигурация слоев, производители рекомендуют использовать четко определенные стеки слоев, изготовление которых хорошо отработано и позволяет получить на выходе надежные и качественные изделия. Далее LTCC-модули тестируются и встраиваются в аппаратуру.

Обычно LTCC-модули строятся из отдельных функциональных блоков, каждый из которых выполняет свою функцию, например, частотное разделение сигналов, коммутацию, усиление и т. д. Такие блоки могут выступать в роли малошумящих усилителей, предусилителей для выходных усилителей мощности, а в более сложных вариантах и в качестве синтезаторов частоты, приемных трактов с преобразованием вниз или вообще законченных приемников. Естественно, что в этом случае блоки включают не только интегрированные LTCC-элементы, но и навесные RFICустройства. Для многодиапазонных приложений мобильной связи функциональность RFIC-устройств может быть еще более сложной, а набор полупроводниковых технологий достаточно широк: GaAs, InP, Si и SiGe.

Вполне очевидно, что в разработке подобных LTCC-приложений будет принимать участие не один инженер, а в общем случае каждый отдельный функциональный блок будет представлять собой отдельную задачу проектирования для конкретного человека. Это накладывает определенные требования на выбор средств проектирования, а также требует, чтобы поток проектирования прежде всего был одобрен всей группой разработчиков. Ряд больших компаний имеют достаточно ресурсов для разработки не только LTCC-модулей, но и RFIC-кристаллов, что дает им большую свободу в поиске оптимального решения по размещению пассивных элементов, отводу тепла, трассировке сигнальных цепей, подводке питания и сигналов управления. Для многих компаний была поставлена «задача максимум» — полное освоение технологии «система на кристалле» (SoC), но на практике оказалось, что технологии низкотемпературной керамики (LTCC) и многокристальных модулей (МСМ) обеспечивают наиболее оптимальное решение, так как позволят выбрать кристаллы или от определенного производителя, или выполненные по наиболее подходящей технологии.

Несмотря на это, разработчики LTCC-модулей столкнулись с рядом проблем, связанных с реализацией LTCC-подложек, а также их интеграцией с широким набором компонентов для поверхностного монтажа. Легко видеть, что технология LTCC представляет собой не просто способ обеспечения связей между навесными компонентами на многослойной плате. Полученные с ее помощью резисторы, катушки индуктивности, конденсаторы и симметрирующие устройства могут быть интегрированы непосредственно в подложку, а это позволяет существенно сократить используемое количество дискретных SMD-компонентов для обеспечения требуемой функциональности. Эти интегрированные элементы должны быть промоделированы в процессе проектирования не только как отдельные обособленные элементы, но и с учетом их близости на подложке с реальными параметрами и размерами. Таким образом, для групп разработчиков одинаково важно качественное моделирование и интегрированных LTCC-элементов, и навесных SMD-компонентов.

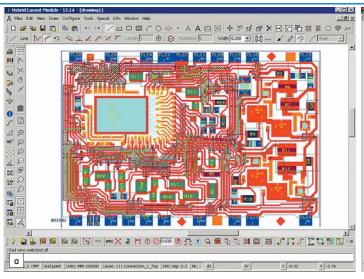

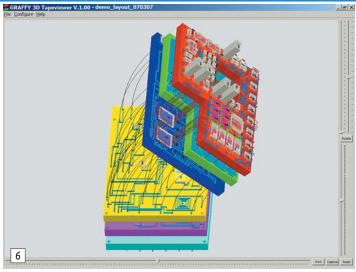

Рис. 3. Разработка топологии LTCC-модуля и верификация его послойной структуры в продукте HYDE

Традиционные EDA-средства обычно ориентированы или на разработку обычных многослойных печатных плат (РСВ), или топологий микросхем (ІС), что не совсем хорошо подходит для проектирования LTCCмодулей. Несмотря на то, что LTCC-модули совмещают в себе некоторые характеристики высокоплотных печатных плат и некоторые специфические особенности интегральных схем, методологии их моделирования должны отличаться от стандартных. Ряд фирм предлагают весьма удачные решения для проектирования LTCC-устройств, как, например, упомянутая ранее фирма Durst (рис. 3), но с ростом рабочих частот появляются проблемы, которые можно разбить на три категории: проблемы моделирования, проблемы разработки топологии и проблемы интеграции средств топологического проектирования и средств моделирования.

Необходимость разработки объемных схем, включающих в себя многослойные межсоединения, скрытые схемные элементы и навесные SMD-компоненты, накладывает на EDA-инструменты определенные требования: наличие точной библиотеки компонентов, наличие модуля электромагнитного (ЕМ) анализа, наличие модуля анализа нелинейных схем, предназначенного для работы со сложными RFIC-схемами, а также наличие мощного графического редактора топологий. Так как здесь практически нет ограничений на размещение проводников на слоях подложки, среда проектирования должна обеспечивать не только их быструю прорисовку, но и гибкие возможности назначения моделей межсоединений. Другими словами, разработчик должен иметь возможность быстрого определения, когда проводник может рассматриваться как идеальное соединение (например, линии подвода питания), а когда как сложная микрополосковая линия, работающая с сигналами на частотах нескольких гигагерц.

Разумеется, это не является универсальным требованием. Для некоторых конфигураций элементов специальное представление межсоединений может не потребоваться вовсе, например, когда элементы соединяются непо-

средственно друг с другом. Другой случай, когда проводники не требуются, это случай близко расположенных конденсаторов, использующих одинаковые электрические узлы и проводники, что позволяет отказаться от дополнительных проводников и соответствующих моделей межсоединений. Тем не менее, в идеальном случае разработчик должен иметь доступ к разным способам моделирования межсоединений. Тогда он будет иметь возможность выбора компромиссного варианта, основываясь на точности вычислений и их ресурсоемкости.

Несмотря на то, что большинство современных систем проектирования включают модели одиночных и связанных линий передач, геометрическая сложность топологии LTCC-модулей требует полного электромагнитного моделирования, так как стандартных моделей и методов экстракции паразитных связей может быть недостаточно. Электромагнитный анализ является не только прекрасным средством проверки проекта, но в общем случае он может быть скомбинирован в рамках интегрированной среды с системой моделирования схем, что даст возможность настройки и оптимизации проекта.

Кроме того, среда проектирования должна позволять выполнять статистический анализ проекта с учетом вариаций в рамках технологических допусков, что позволит оценить возможные проблемы, связанные с массовым выпуском LTCC-модулей. Электромагнитное моделирование отдельного схемного элемента может быть выполнено ЕМ вычислителем первичного уровня, комбинация нескольких элементов, по сути представляющая собой функциональный блок (например, диплексер), потребует более мощного вычислителя. Анализ же законченного LTCC-модуля может потребовать использования еще более продвинутых средств ЕМ-анализа. Другими словами, ЕМ-моделирование в LTCC-индустрии представляет собой широкое поле для исследований, результаты которых могут повлиять на оптимальный выбор процессоров и объем памяти, необходимой для моделирования законченных LTCC-модулей.

Для эффективного проектирования наиболее часто встречающиеся элементы схем должны быть сгруппированы в специальных библиотеках. Формы построения таких библиотек и способы работы с ними являются темой непрерывных дискуссий в LTCC-индустрии, однако разглашение деталей ограничено, как правило, двусторонними соглашениями между производителями LTCC-модулей и разработчиками программного обеспечения. Удивляться тут нечему, так как главной целью каждого проекта в области телекоммуникаций является своевременный выход изделия на рынок и его конкурентоспособность. Ниже мы постараемся рассмотреть общие процедуры построения технологических библиотек, не затрагивая чьих-либо коммерческих интересов.

Библиотеки, ориентированные на определенный технологический процесс, как это принято в ММІС- и ІС-индустрии, называются технологическими библиотеками (Process Design Kit, PDK). Разработка РDК-библиотек представляет собой построение пользовательской библиотеки элементов и моделей для определенной системы проектирования с учетом какой-либо конкретной технологии изготовления этих компонентов. Рассмотрим, как данная задача решена в системе проектирования AWR Microwave Office компании Applied Wave Research (www.awrcorp.com).

PDK-библиотека учитывает стек слоев, выполняет согласование слоев между средствами топологического проектирования и ЕМмоделирования, а также определяет слои, на которых компоненты могут соединяться между собой. Соответствие между слоями с прорисованным рисунком металлизации и реальными диэлектрическими слоями описывается специальными технологическими LPF-файлами. В дальнейшем информация из этих файлов будет использована средствами прорисовки топологии и моделирования для синхронизации размещения компонента в стеке слоев, а также для финальной передачи проекта в систему ЕМ-моделирования окончательной верификации.

Например, в среде AWR Design Environment для построения библиотек используется струк-

#### Технологии в электронной промышленности, № 3′2008

турированный язык XML. PDK использует ХМС-библиотеку для описания связей между схемотехническими моделями, топологическим представлением компонентов, специальными символами элементов и ссылками на библиотеки навесных SMD-компонентов. Доступ к библиотеке осуществляется через окно просмотра, порядок отображения данных в котором определяется структурой ХМСфайла. Таким образом, разработчик получает универсальную среду проектирования, позволяющую выбрать интегрированные и навесные компоненты из специальных упорядоченных наборов. Дополнительное удобство заключается в том, что и интегрированные, и навесные элементы прорисовываются в одном редакторе.

Благодаря наличию интегрированных и навесных компонентов, ассоциированных вместе в конкретной технологической библиотеке, разработчик может быть уверен, что при добавлении на топологию любого интегрированного компонента он будет соединен с нужным SMD-компонентом, а вся группа компонентов будет иметь правильное размещение в стеке слоев по оси Z.

Модели схемотехнических элементов можно разбить на два класса: аналитические и эмпирические. В общем случае каждый элемент может быть описан обеими моделями, а выбор конкретной модели предполагается на усмотрение пользователя. Для начала обсудим моделирование спиральной катушки индуктивности, показанной на рис. 4.

В среде проектирования AWR Design Environment процесс создания модели занимает два этапа. Прежде всего, структура спирали прорисовывается как набор примитивов, представляющих собой связанные линии, расположенные на разных слоях, моделирование которых возможно с помощью встроенного квазистатического 2D ЕМ-вычислителя для поперечного сечения подложки. Такая модель будет учитывать связи только между параллельными сегментами спирали. После того как инженер, ответственный за разработку модели, убедится, что она функционирует как следует, он с помощью специальной программы AWR Model Wizard в автоматическом режиме

сформирует С++ код, по сути представляющий собой процедуру прорисовки катушки по заранее определенному набору ее основных параметров и топологии. Сформированный С++ код компилируется, в результате чего формируется исполняемая DLL-библиотека, содержащая описание катушки.

На следующем этапе полученная DLL-библиотека сохраняется в специальной директории моделей определенного набора технологических библиотек PDK. Использоваться она будет только при следующем запуске программы Microwave Office. Далее при добавлении данной модели катушки на схему или топологию программный код, реализованный в DLLфайле, автоматически нарисует ее на соответствующих слоях согласно описанию в LTCC технологических файлах. Инженер, занимающийся разработкой библиотеки, также может создать специальный символ, с помощью которого данный элемент будет отображаться на схеме, и добавить файл справки, описывающий особенности использования данного элемента (возможные ограничения, частотный диапазон и т. д.). Все эти части описания элемента будут представлены в ХМL-библиотеке в структурированной форме.

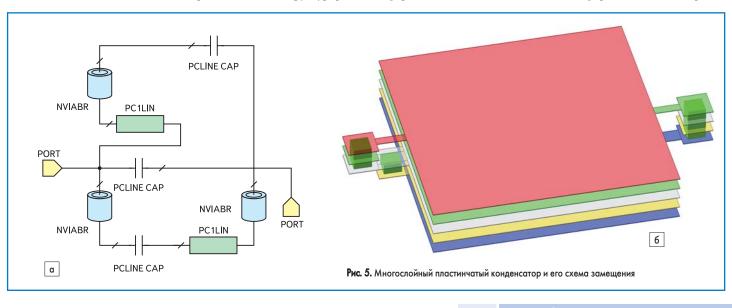

Модель многослойного пластинчатого конденсатора построена аналогичным образом. Электрическое представление конденсатора реализовано как схема замещения, содержащая модели линий передач, межслойных переходов и конденсаторов из библиотеки стандартных элементов (рис. 5). По данной схеме замещения AWR Model Wizard сформирует С++ процедуру, которая после компиляции и добавления в библиотеку будет формировать на топологии нужный набор примитивов. Остается лишь добавить к модели схемотехнический символ и файл справки.

Описанная выше компилированная библиотека предоставляет конечному пользователю, а также LTCC-производителям ряд преимуществ, например производительность, точность, возможность распространения и защиту прав интеллектуальной собственности. С точки зрения производительности компилированная модель работает быстрее интерпретированной версии той же модели. Кроме того, так как такая модель базируется на принципах электродинамики, то она дает более точный результат и работает в более широком динамическом диапазоне, чем модель, описанная в аналитической форме и имеющая ограни-

ченный набор данных. Дополнительным преимуществом является то, что компилированная DLL-библиотека имеет небольшой размер, что позволяет без особых затрат пересылать ее по электронной почте в случае внесения изменений в технологический процесс или обновления самой модели. И, наконец, скомпилированная модель является более защищенной, так как третьи лица не могут относительно просто ее декомпилировать и заимствовать исходный код.

Второй способ построения моделей предполагает эмпирический подход. Набор данных, описывающих компонент в пространстве физических параметров, строится по результатам электродинамического моделирования. Доступ к данным модели осуществляется через механизм индексации, где каждый индекс ссылается на соответствующий физический параметр. Механизм интерполяции устраняет дискретность модели. Основное преимущество использования эмпирических данных заключается в высокой точности расчета, но в ряде случаев оно предполагает некоторые ограничения для пользователей.

Оба подхода к построению наборов моделей для библиотек компонентов имеют свои преимущества и широко используются многими группами разработчиков. Но все они имеют одно неудобство, связанное с ограниченным набором графических примитивов, используемых для прорисовки топологии компонента. В ряде случаев обеспечение определенных электрических параметров может потребовать от модели не просто изменения размеров или положения прямоугольных примитивов. К сожалению, сейчас маловероятно, что в библиотеки компонентов будут добавлены нестандартные графические примитивы, скорее всего, в PDK будут присутствовать лишь квадраты и прямоугольники с ограниченным коэффициентом пропорциональности.

Сейчас при разработке нового компонента будет использоваться следующий сценарий. Сначала на подложке заданного типа рисуется проводник нужной формы, затем он моделируется ЕМ-вычислителем и оптими-

зируется посредством добавления или удаления частей металлизации, пока не будут обеспечены требуемые электрические параметры. Например, для L-образного конденсатора программа ЕМ-моделирования рассчитывает набор S-параметров, по ним рассчитывается эквивалентная емкость, величина которой сравнивается с прототипом. По мере увеличения размеров конденсатора он становится сравнимым с длиной волны и за счет паразитной индуктивности получает зависимость эквивалентной емкости от частоты, о чем разработчику необходимо знать как можно раньше. Выявление подобных паразитных эффектов не является уникальной задачей для данного подхода, так как для большинства компонентов работает общее правило, согласно которому, чем больший компонент становится по сравнению с длиной волны в диэлектрике, тем более выражены в нем паразитные параметры.

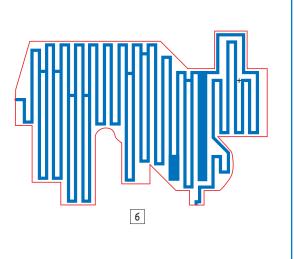

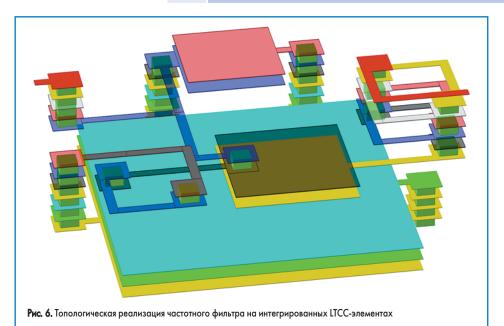

При наличии законченной и проверенной технологической библиотеки можно приступать к разработке LTCC-функционального блока или законченного модуля. Рассмотрим пример разработки фильтра с заданными частотными характеристиками. Для разработки фильтра прототипа используется обычная технология синтеза фильтра на сосредоточенных элементах. По номиналам элементов формируются физические интегрированные элементы, которые затем моделируются с использованием технологической информации из PDK, встроенной в модель.

На следующем этапе делается оценка параметров фильтра с учетом отклонений значений, паразитных параметров моделей и взаимных связей между близко расположенными элементами (рис. 6). Паразитные эффекты внутри моделей будут легко обнаружены на этапе моделирования схемы. Влияние технологических допусков и взаимных связей между компонентами может быть оценено только в процессе ЕМ-моделирования. Некоторые инженеры, работающие в данной области, предпочитают группировать все проблемы вместе и оценивать их только с помощью ЕМ-моделирова-

ния, так как на практике эффекты, связанные с близостью компонентов и точностью их изготовления, доминируют над паразитными эффектами внутри самих компонентов. А раз ЕМ-вычислитель дает более точный результат, чем схемотехническое моделирование, следующий этап проектирования предполагает его интенсивное использование.

Несмотря на то, что ЕМ-вычислители на основе метода моментов (Method of moment, MoM) доступны в двух исполнениях: сеточном и бессеточном, опыт показывает, что сеточные методы демонстрируют большую точность и динамический диапазон по сравнению с бессеточными методами, более гибкими в смысле представления геометрии [2]. Использование встроенных оптимизаторов предполагает работу с непрерывными функциями, описывающими конечные значения параметров, а при оптимизации топологии ее элементы могут варьироваться лишь дискретно согласно шагу сетки разбиения.

Таким образом, перед пользователем стоит проблема выбора: использовать ли мелкие сетки разбиения и получать большое время моделирования или относительно быстро получать неточный результат, связанный с дискретизацией значений размеров графических примитивов и рассогласованием моделируемой структуры с сеткой моделирования. Этот источник ошибки может быть частично или полностью подавлен за счет использования специальных дискретных алгоритмов оптимизации, которые подстраивают вариации параметров структуры для максимального согласования с сеткой разбиения ЕМ-вычислителя.

С появлением открытых вычислительных технологий, таких как Microsoft Component Object Model (COM), стала возможной интеграция программ моделирования различных производителей в рамках единой среды проектирования. Компания AWR предлагает клиентам интерфейс EM Socket, который использует СОМ-технологию и дает возможность моделировать ЕМ-структуры не только во встроенном собственном вычислителе EMSight, но и в системах электромагнитного моделирования третьих фирм, что дает возможность разработчикам проверить результаты, полученные с помощью разных методов моделирования. В случае с показанным на рис. 6 фильтром, из-за того, что он имеет электрически малые размеры, для его анализа будет достаточно встроенного ЕМ-вычислителя. По мере увеличения размеров анализируемой структуры имеет смысл использовать внешнюю систему моделирования, например пакет Sonnet Suite компании Sonnet Software (www.sonnetsoftware.com).

Несмотря на то, что программы моделирования планарных структур быстро развиваются, задача оптимизации пассивных функциональных блоков все еще представляет собой относительно сложную задачу. На смену грубым методам оптимизации «в лоб» приходят новые адаптивные методы, например, метод принудительного разбиения или декомпозиции (Aggressive Space Mapping and Decomposition), который комбинирует взаимодействие про-

## I

#### Технологии в электронной промышленности, № 3′2008

грамм схемотехнического и электромагнитного моделирования. Остается добавить, что этот метод использует ЕМ-вычислитель очень ограниченно, а значит, работает максимально быстро и эффективно.

При моделировании функциональных LTCCблоков с ростом числа навесных SMD-компонентов появляются новые проблемы. Если моделирование чип конденсаторов, катушек индуктивности, диодов и небольших СВЧмонолитных микросхем (ММІС) не вызывает особых проблем, то при использовании сложных СВЧ-микросхем (RFIC) оно значительно затрудняется из-за отсутствия качественной модели. Дело в том, что многие производители предоставляют пользователям документацию с ограниченным описанием своих изделий, и этой информации достаточно лишь для построения грубых поведенческих моделей для оценки уровней сигналов в частотной области в нелинейном режиме. В том случае, если RFIC-микросхемы используют перенос частоты, их моделирование становится достаточно сложной задачей.

Возможным решением для столь сложных задач может служить использование моделирования на схемотехническом уровне. Концепция построения схемных моделей таких функциональных модулей была показана на примере интегрированных LTCC-компонентов, она может быть применена и для более сложных компонентов. Если специалисты фирмы — производителя LTCC-устройств — имеют четкое описание технологии проектирования RFIC-устройств, в этой задаче нет ничего сверхсложного. Такой способ моделирования становится очень интересным и привлекательным даже для случаев, когда группы LTCC- и RFIC-разработчиков работают на разные компании. Единственное что для этого требуется, это чтобы обе стороны работали в одной и той же среде проектирования.

### **Новости EDA Expert**

+\*\*

Компания Zuken сообщила о выходе продукта CADSTAR E3.Logic. По сути, новый продукт представляет собой интеграцию популярной среды проектирования печатных плат CADSTAR с программой E3.Logic, входящей в набор программ E3.series, ранее разработанной немецкой фирмой CIM-Team. В апреле 2006 года эта фирма была поглощена компанией Zuken и начала работы по интеграции своих продуктов в линейку продуктов CADSTAR, постепенно объединяя два разных направления: электротехническое проектирование и разработку печатных плат.

В итоге, пакет CADSTAR получил альтернативный редактор схем, использующий единую базу данных компонентов, что существенно упрощает обмен данными с MRP-, ERP- и PDM-системами.

\*\*\*

Компания CST сообщила о выходе двух новых продуктов: CST PCB STUDIO и CST CABLE STUDIO. Оба продукта предназначены для моделирования ЕМС-и ЕМІ-эффектов в печатных платах и кабелях соответственно.

CST PCB STUDIO может быть интегрирован в различные потоки проектирования и позволяет выполнять анализ целостности сигналов и перекрестных искажений на высокоскоростных цифровых, смешанных аналого-цифровых платах, а также в источниках питания. Особый интерес представляет интерфейс с программой CST MICROWAVE STUDIO, что дает возможность выполнять полный трехмерный анализ электромагнитных излучений на плате.

CST CABLE STUDIO фокусируется на моделировании кабелей и позволяет оптимизировать вес и размер одиночных проводов, витых пар, а также сложных жгутов с неограниченным числом проводников. Программа дает возможность оценивать напряжения в разных точках кабелей, токи через определенные проводники, S-параметры, импедансы, а также, благодаря интеграции с CST MICROWAVE STUDIO, — взаимные наводки проводников друг на друга.

\*\*\*

Компания KONEKT SPRL сообщила о выходе новой версии автотрассировщика ELECTRA v2. В новую версию внесены следующие изменения:

- Расширена иерархия правил проектирования. Добавлена категория правил Rules-by-Area, определяющая ширину проводников и зазоры для определенных областей платы с помощью специального редактора.

- Введено диалоговое окно определения стратегии трассировки.

- Доработан пользовательский интерфейс. Введена панель управления отображением слоев и объектов. Введена панель статистики, измерительная линейка, средства интерактивного выбора цепей.

- Реализована функция масштабирования с помощью колеса мыши.

- Улучшены возможности отображения слоев. Теперь отображаются контуры полигонов и слепые/скрытые переходные отверстия.

Введена возможность отмены и перезапуска процесса трассировки, что позволяет проверить различные стратегии.

\*\*

Австралийская компания Altium Limited анонсировала очередное обновление системы проектирования печатных плат — Altium Designer 6.9.

Основные изменения коснулись средств 3D-визуализации платы. Стало возможным отображать одновременно несколько трехмерных видов платы, назначать отдельные цвета объектам на разных слоях, а также отображать тени. Значительно доработан интерфейс обмена данными с механическими системами проектирования через формат STEP, который используется для импорта реалистичных 3D-моделей компонентов и экспорта конечного проекта платы. Кроме того, добавлена возможность копирования трехмерного вида в буфер обмена Windows в графической форме.

\*\*

Компания Altium официально сообщила о дате прекращения поддержки своего продукта P-CAD 2006. Летом 2006 года компания заявила, что планирует прекратить развитие линии продуктов для проектирования печатных плат P-CAD. Вышедшая в тот момент версия P-CAD 2006 должна стать последней в истории этого продукта, а всем пользователям будет предложено перейти на другой, более мощный продукт фирмы — Altium Designer.

За прошедшие неполные два года фирма выпустила всего два сервис-пака для продукта P-CAD, которые включали лишь небольшие исправления найденных критических ошибок, и серьезно продукт не развивала. В начале мая появилось сообщение о полном прекращении поддержки продукта P-CAD после 30 июня 2008 года. Для пользователей это будет означать следующее: текущие контракты на техническую поддержку продлеваться не будут, а также не будут заключаться новые контракты.

Для российских пользователей продукта, которые традиционно не пользуются фирменной англоязычной технической поддержкой, более важным является тот факт, что после 30 июня нельзя будет легально приобрести продукт серии Р-САD. Это означает, что предприятия, в силу исторических причин сейчас работающие на нелицензионных продуктах АССЕL EDA и Р-САD 200х, после 30 июня 2008 года не смогут легализоваться без перехода на другой продукт.

Чтобы сгладить проблему миграции, фирма Altium бросила все силы на развитие своего ключевого продукта Altium Designer (ранее Protel). Версия 6 претерпела уже 9 существенных обновлений, в результате которых был существенно доработан автотрассирощик Situs, а также впервые в истории электронных САПР была сделана официальная русификация пакета. Последний факт должен сделать продукт весьма привлекательным для российского рынка. На лето 2008-го запланирован выход новой версии пакета, которая получила название Altium Designer Summer 08.